Существует два типа элементов памяти, основанных на типе запуска, который подходит для его работы.

- Задвижки

- Шлепки

Защелки работают с разрешающим сигналом, который чувствителен к уровню . Принимая во внимание, что шлепанцы чувствительны к краям. Мы поговорим о шлепанцах в следующей главе. Теперь давайте поговорим о SR Latch & D Latch один за другим.

SR Latch

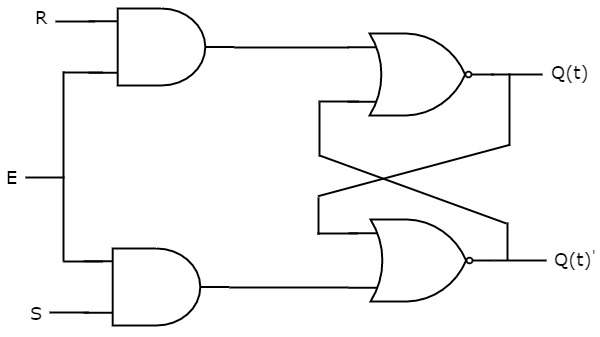

SR Latch также называется Set Reset Latch . Эта защелка влияет на выходы до тех пор, пока активация E поддерживается на уровне «1». Принципиальная электрическая схема SR Latch показана на следующем рисунке.

Эта схема имеет два входа S & R и два выхода Q (t) и Q (t) ‘. Верхний вентиль NOR имеет два входа R & дополнение текущего состояния, Q (t) ‘, и выдает следующее состояние, Q (t + 1), когда разрешено, E равно’ 1 ‘.

Аналогично, нижний логический элемент NOR имеет два входа S и текущее состояние, Q (t), и выдает дополнение следующего состояния, Q (t + 1) ‘, когда разрешено, E равно’ 1 ‘.

Мы знаем, что вентиль NOR с 2 входами производит выход, который является дополнением к другому входу, когда один из входов равен «0». Точно так же это производит ‘0’ вывод, когда один из входных данных ‘1’.

-

Если S = 1, то следующее состояние Q (t + 1) будет равно «1» независимо от текущего состояния, значения Q (t).

-

Если R = 1, то следующее состояние Q (t + 1) будет равно «0» независимо от текущего состояния, значения Q (t).

Если S = 1, то следующее состояние Q (t + 1) будет равно «1» независимо от текущего состояния, значения Q (t).

Если R = 1, то следующее состояние Q (t + 1) будет равно «0» независимо от текущего состояния, значения Q (t).

В любое время только из этих двух входов должно быть «1». Если оба входа имеют значение «1», то значение следующего состояния Q (t + 1) не определено.

В следующей таблице показана таблица состояний SR-защелки.

| S | р | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (T) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | — |

Поэтому SR Latch выполняет три типа функций, таких как Hold, Set & Reset, в зависимости от условий ввода.

D Latch

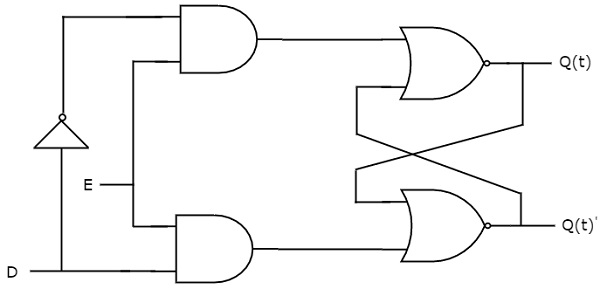

Есть один недостаток SR Latch. То есть следующее значение состояния не может быть предсказано, когда оба входа S & R едины. Таким образом, мы можем преодолеть эту трудность с помощью D Latch. Это также называется Data Latch. Принципиальная схема D Latch показана на следующем рисунке.

Эта схема имеет один вход D и два выхода Q (t) и Q (t) ‘. D Latch получается из SR Latch, помещая инвертор между входами S amp & & R и подключая вход D к S. Это означает, что мы исключили комбинации S & R одинакового значения.

-

Если D = 0 → S = 0 & R = 1, то следующее состояние Q (t + 1) будет равно «0» независимо от текущего состояния, значения Q (t). Это соответствует второй строке таблицы состояний SR Latch.

-

Если D = 1 → S = 1 & R = 0, то следующее состояние Q (t + 1) будет равно «1» независимо от текущего состояния, значения Q (t). Это соответствует третьей строке таблицы состояний SR Latch.

Если D = 0 → S = 0 & R = 1, то следующее состояние Q (t + 1) будет равно «0» независимо от текущего состояния, значения Q (t). Это соответствует второй строке таблицы состояний SR Latch.

Если D = 1 → S = 1 & R = 0, то следующее состояние Q (t + 1) будет равно «1» независимо от текущего состояния, значения Q (t). Это соответствует третьей строке таблицы состояний SR Latch.

В следующей таблице показана таблица состояний D-защелки.

| D | Q (t + 1) |

|---|---|

| 0 | 0 |

| 1 | 1 |

Таким образом, D Latch Удерживает информацию, которая доступна на входе данных, D. Это означает, что выход D Latch чувствителен к изменениям на входе, D, пока разрешение является Высоким.

В этой главе мы реализовали различные защелки, обеспечив перекрестную связь между воротами NOR. Точно так же вы можете реализовать эти защелки с помощью вентилей NAND.