Мы знаем, что один триггер может хранить один бит информации. Чтобы хранить несколько битов информации, нам нужно несколько триггеров. Группа триггеров, которые используются для хранения (хранения) двоичных данных, называется регистром .

Если регистр способен сдвигать биты либо вправо, либо влево, это называется регистром сдвига . Регистр сдвига битов «N» содержит триггеры «N». Ниже приведены четыре типа регистров сдвига, основанные на применении входов и доступе к выходам.

- Serial In — сдвиговый регистр Serial Out

- Серийный вход — параллельный выходной регистр сдвига

- Параллельный вход — сдвиговый регистр последовательного выхода

- Параллельный вход — сдвиговый регистр параллельного выхода

Серийный вход — Серийный выход (SISO) Сдвиговый регистр

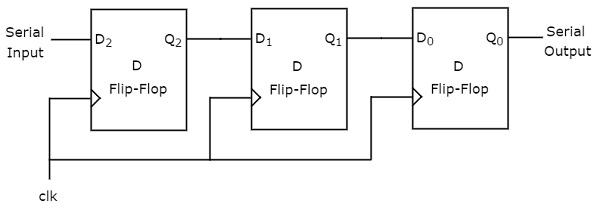

Сдвиговый регистр, который допускает последовательный ввод и производит последовательный вывод, известен как сдвиговый регистр Serial In — Serial Out (SISO) . Блок-схема 3-битного регистра сдвига SISO показана на следующем рисунке.

Эта блок-схема состоит из трех D-триггеров, которые каскадируются . Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно со входа самого левого D-триггера. Следовательно, этот вход также называется последовательным входом . При каждом срабатывании положительного фронта тактового сигнала данные перемещаются с одной ступени на другую. Таким образом, мы можем получать биты последовательно с выхода самого правого D-триггера. Следовательно, этот выход также называется последовательным выходом .

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SISO, посылая двоичную информацию «011» из LSB в MSB последовательно на входе.

Предположим, что начальный статус D-триггеров слева направо равен Q2Q1Q0=000. Мы можем понять работу 3-битного регистра сдвига SISO из следующей таблицы.

| Нет положительного края часов | Последовательный ввод | Q 2 | Q 1 | Q 0 |

|---|---|---|---|---|

| 0 | — | 0 | 0 | 0 |

| 1 | 1 (LSB), | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (СЗБ) | 0 | 1 | 1 (LSB), |

| 4 | — | — | 0 | 1 |

| 5 | — | — | — | 0 (СЗБ) |

Начальное состояние D-триггеров в отсутствие тактового сигнала: Q2Q1Q0=000. Здесь последовательный вывод исходит из Q0. Таким образом, LSB (1) принимается на 3- м положительном фронте тактового сигнала, а MSB (0) принимается на 5- м положительном фронте тактового сигнала.

Следовательно, 3-битный сдвиговый регистр SISO требует пяти тактовых импульсов для получения действительного выхода. Аналогично, N-битный сдвиговый регистр SISO требует 2N-1 тактовых импульсов для сдвига «N» битовой информации.

Сдвиговый регистр Serial In — Parallel Out (SIPO)

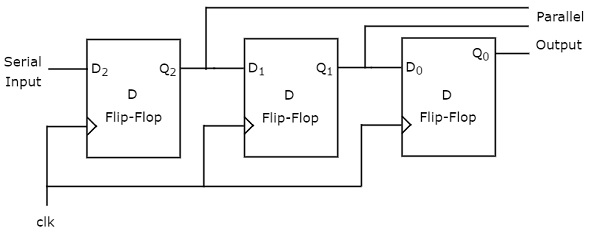

Сдвиговый регистр, который допускает последовательный ввод и производит параллельный вывод, известен как сдвиговый регистр Serial In — Parallel Out (SIPO) . Блок-схема 3-битного регистра сдвига SIPO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно со входа самого левого D-триггера. Следовательно, этот вход также называется последовательным входом . При каждом срабатывании положительного фронта тактового сигнала данные перемещаются с одной ступени на другую. В этом случае мы можем получить доступ к выходам каждого D триггера параллельно. Итак, мы получим параллельные выходы из этого регистра сдвига.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SIPO, посылая двоичную информацию «011» из LSB в MSB последовательно на входе.

Предположим, что начальный статус D-триггеров слева направо равен Q2Q1Q0=000. Здесь Q2 & Q0 — это MSB и LSB соответственно. Мы можем понять работу 3-битного сдвигового регистра SIPO из следующей таблицы.

| Нет положительного края часов | Последовательный ввод | Q 2 (MSB) | Q 1 | Q 0 (LSB) |

|---|---|---|---|---|

| 0 | — | 0 | 0 | 0 |

| 1 | 1 (LSB), | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (СЗБ) | 0 | 1 | 1 |

Начальное состояние D-триггеров в отсутствие тактового сигнала: Q2Q1Q0=000. Двоичная информация «011» получается параллельно на выходах D триггеров для третьего положительного фронта тактового сигнала.

Итак, 3-битный сдвиговый регистр SIPO требует три тактовых импульса для получения действительного выхода. Аналогично, N-битный сдвиговый регистр SIPO требует N тактовых импульсов для сдвига «N» битовой информации.

Сдвиговый регистр параллельного входа — последовательного выхода (PISO)

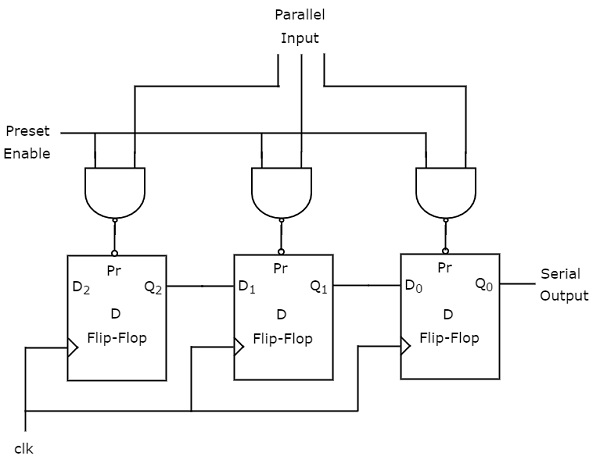

Сдвиговый регистр, который допускает параллельный ввод и производит последовательный выход, известен как сдвиговый регистр Parallel In-Serial Out (PISO) . Блок-схема 3-битного регистра сдвига PISO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить параллельные входы к каждому D-триггеру, установив Preset Enable в 1. Для каждого срабатывания положительного фронта тактового сигнала данные сдвигаются от одного этапа к следующему. Итак, мы получим последовательный вывод с самого правого D-триггера.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига PISO, применяя двоичную информацию «011» параллельно через предустановленные входы.

Так как предустановленные входные данные применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого к правому будет Q2Q1Q0=011. Мы можем понять работу 3-битного регистра сдвига PISO из следующей таблицы.

| Нет положительного края часов | Q 2 | Q 1 | Q 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 (LSB), |

| 1 | — | 0 | 1 |

| 2 | — | — | 0 (LSB) |

Здесь последовательный вывод исходит из Q0. Таким образом, LSB (1) принимается до применения положительного фронта тактового сигнала, а MSB (0) принимается на 2- ом положительном фронте тактового сигнала.

Следовательно, 3-битный регистр сдвига PISO требует двух тактовых импульсов для получения действительного выхода. Аналогично, N-битный регистр сдвига PISO требует N-1 тактовых импульсов, чтобы сдвигать N-битную информацию.

Регистр сдвига параллельного входа — параллельного выхода (PIPO)

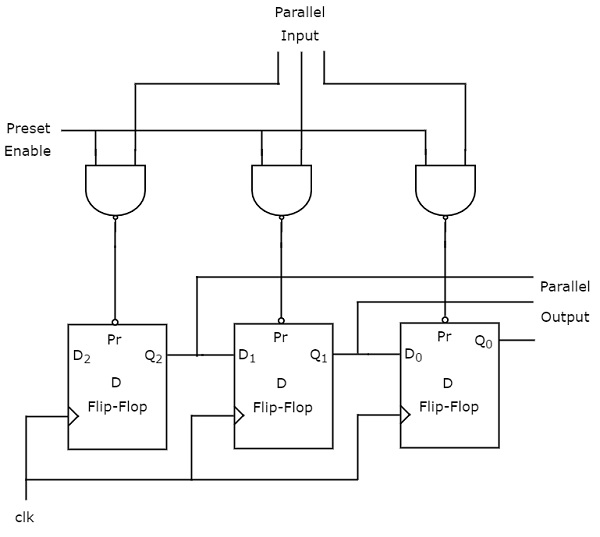

Сдвиговый регистр, который допускает параллельный ввод и производит параллельный вывод, известен как сдвиговый регистр Parallel In — Parallel Out (PIPO) . Блок-схема 3-битного регистра сдвига PIPO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить параллельные входы к каждому D-триггеру, установив Preset Enable в 1. Мы можем применить параллельные входы через предустановку или сброс. Эти два являются асинхронными входами. Это означает, что триггеры производят соответствующие выходные данные, основываясь на значениях асинхронных входных данных. В этом случае влияние выходов не зависит от тактового перехода. Итак, мы получим параллельные выходы от каждого D-триггера.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига PIPO, применяя двоичную информацию «011» параллельно через предустановленные входы.

Так как предустановленные входные данные применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого к правому будет Q2Q1Q0=011. Таким образом, двоичная информация «011» получается параллельно на выходах D триггеров перед применением положительного фронта тактового сигнала.

Следовательно, 3-битный регистр сдвига PIPO требует нулевых тактовых импульсов для получения действительного выхода. Аналогично, N-битный регистр сдвига PIPO не требует никакого тактового импульса для сдвига информации «N» битов.