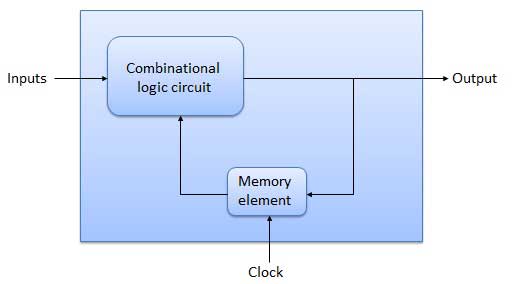

Комбинационная схема не использует никакой памяти. Следовательно, предыдущее состояние входа не влияет на текущее состояние схемы. Но последовательная схема имеет память, поэтому выходной сигнал может варьироваться в зависимости от входа. Этот тип схем использует предыдущий вход, выход, часы и элемент памяти.

Блок-схема

Резкий поворот

Триггер — это последовательная схема, которая обычно производит выборку своих входов и изменяет свои выходы только в определенные моменты времени, а не непрерывно. Считается, что триггер чувствителен к краям или срабатывает по краям, а не по уровню, как защелки.

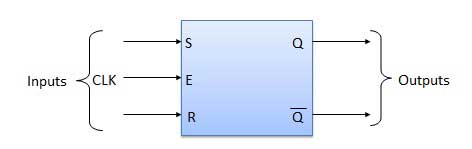

SR флип-флоп

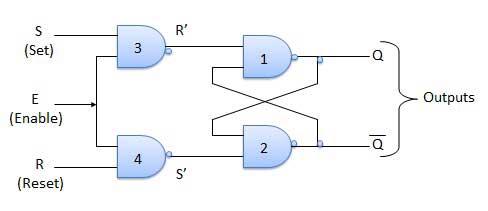

В основном это SR-защелка с использованием NAND-вентилей с дополнительным входом включения . Он также называется уровнем срабатывания SR-FF. Для этого цепь на выходе будет иметь место тогда и только тогда, когда активирован вход разрешения (E). Короче говоря, эта схема будет работать как SR-защелка, если E = 1, но нет изменений в выходе, если E = 0.

Блок-схема

Принципиальная электрическая схема

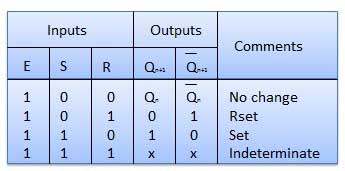

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | S = R = 0: без изменений |

Если S = R = 0, то выходные данные вентилей NAND 3 и 4 принудительно становятся равными 1. Следовательно, R ‘и S’ оба будут равны 1. Поскольку S ‘и R’ являются входом базовой SR-защелки с использованием вентилей NAND, состояние выходов не изменится. |

| 2 | S = 0, R = 1, E = 1 |

Поскольку S = 0, выход NAND-3, т. Е. R ‘= 1, а E = 1, выход NAND-4, т. Е. S’ = 0. Следовательно, Q n + 1 = 0 и Q n + 1 бар = 1. Это условие сброса. |

| 3 | S = 1, R = 0, E = 1 |

Выход NAND-3, т. Е. R ‘= 0, и выход NAND-4, т. Е. S’ = 1. Следовательно, выход SR NAND защелки имеет значение Q n + 1 = 1 и Q n + 1 бар = 0. Это условие сброса. |

| 4 | S = 1, R = 1, E = 1 |

Поскольку S = 1, R = 1 и E = 1, выходные данные вентилей NAND 3 и 4 равны 0, т. Е. S ‘= R’ = 0. Следовательно, состояние гонки будет происходить в базовой защелке NAND. |

Если S = R = 0, то выходные данные вентилей NAND 3 и 4 принудительно становятся равными 1.

Следовательно, R ‘и S’ оба будут равны 1. Поскольку S ‘и R’ являются входом базовой SR-защелки с использованием вентилей NAND, состояние выходов не изменится.

Поскольку S = 0, выход NAND-3, т. Е. R ‘= 1, а E = 1, выход NAND-4, т. Е. S’ = 0.

Следовательно, Q n + 1 = 0 и Q n + 1 бар = 1. Это условие сброса.

Выход NAND-3, т. Е. R ‘= 0, и выход NAND-4, т. Е. S’ = 1.

Следовательно, выход SR NAND защелки имеет значение Q n + 1 = 1 и Q n + 1 бар = 0. Это условие сброса.

Поскольку S = 1, R = 1 и E = 1, выходные данные вентилей NAND 3 и 4 равны 0, т. Е. S ‘= R’ = 0.

Следовательно, состояние гонки будет происходить в базовой защелке NAND.

Мастер Раб JK Флип-флоп

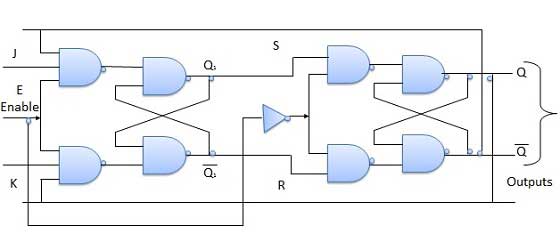

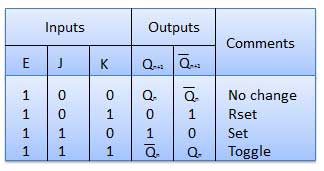

Ведомое ведомое устройство JK FF представляет собой каскад из двух SR FF с обратной связью с выхода секунды на вход первого. Мастер положительный уровень срабатывает. Но из-за присутствия инвертора в линии синхронизации ведомый будет реагировать на отрицательный уровень. Следовательно, когда часы = 1 (положительный уровень), ведущий активен, а ведомый неактивен. Принимая во внимание, что когда часы = 0 (низкий уровень), ведомое устройство активно, а ведущее устройство неактивно.

Принципиальная электрическая схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | J = K = 0 (без изменений) |

Когда часы = 0, ведомый становится активным, а ведущий неактивным. Но поскольку входы S и R не изменились, ведомые выходы также останутся неизменными. Поэтому выходы не изменятся, если J = K = 0. |

| 2 | J = 0 и K = 1 (Сброс) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 0 и Q 1 bar = 1. Это означает, что S = 0 и R = 1. Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 0 и Q bar = 1. Снова часы = 1 — Ведущий активен, подчиненный неактивен. Следовательно, даже если измененные выходы Q = 0 и Q bar = 1 возвращены ведущему, его выход будет Q1 = 0 и Q1 bar = 1. Это означает, что S = 0 и R = 1. Следовательно, когда часы = 0 и ведомое устройство становится активным, выходы ведомого устройства останутся Q = 0 и Q bar = 1. Таким образом, мы получим стабильный выход от ведущего ведомого устройства. |

| 3 | J = 1 и K = 0 (Set) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 1 и Q 1 бар = 0. Это означает, что S = 1 и R = 0. Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 1 и Q bar = 0. Снова clock = 1 — тогда можно показать, что выходы ведомого устройства стабилизируются до Q = 1 и Q bar = 0. |

| 4 | J = K = 1 (Переключить) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Выходы мастера будут переключаться. Так что S и R также будут инвертированы. Часы = 0 — Ведомый активен, ведущий неактивен. Выходы раба будут переключаться. Эти измененные выходные данные возвращаются на главные входы. Но так как часы = 0, мастер по-прежнему неактивен. Таким образом, он не реагирует на эти измененные результаты. Это позволяет избежать многократного переключения, которое приводит к гонке вокруг состояния. Мастер-слейв-флип позволит избежать гонки вокруг условия. |

Когда часы = 0, ведомый становится активным, а ведущий неактивным. Но поскольку входы S и R не изменились, ведомые выходы также останутся неизменными. Поэтому выходы не изменятся, если J = K = 0.

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 0 и Q 1 bar = 1. Это означает, что S = 0 и R = 1.

Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 0 и Q bar = 1.

Снова часы = 1 — Ведущий активен, подчиненный неактивен. Следовательно, даже если измененные выходы Q = 0 и Q bar = 1 возвращены ведущему, его выход будет Q1 = 0 и Q1 bar = 1. Это означает, что S = 0 и R = 1.

Следовательно, когда часы = 0 и ведомое устройство становится активным, выходы ведомого устройства останутся Q = 0 и Q bar = 1. Таким образом, мы получим стабильный выход от ведущего ведомого устройства.

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 1 и Q 1 бар = 0. Это означает, что S = 1 и R = 0.

Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 1 и Q bar = 0.

Снова clock = 1 — тогда можно показать, что выходы ведомого устройства стабилизируются до Q = 1 и Q bar = 0.

Часы = 1 — Ведущий активен, подчиненный неактивен. Выходы мастера будут переключаться. Так что S и R также будут инвертированы.

Часы = 0 — Ведомый активен, ведущий неактивен. Выходы раба будут переключаться.

Эти измененные выходные данные возвращаются на главные входы. Но так как часы = 0, мастер по-прежнему неактивен. Таким образом, он не реагирует на эти измененные результаты. Это позволяет избежать многократного переключения, которое приводит к гонке вокруг состояния. Мастер-слейв-флип позволит избежать гонки вокруг условия.

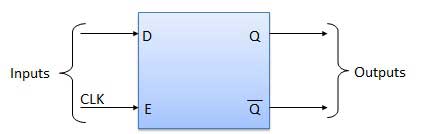

Delay Flip Flop / D Flip Flop

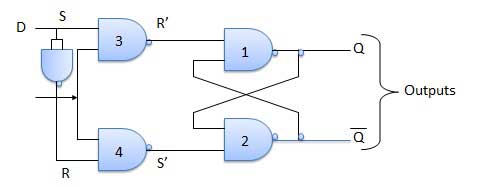

Delay Flip Flop или D Flip Flop — это простая стробированная SR-защелка с инвертором NAND, подключенным между входами S и R. Он имеет только один вход. Входные данные появляются на выходе через некоторое время. Из-за этой задержки данных между i / p и o / p это называется задержкой триггера. S и R будут дополнять друг друга благодаря инвертору NAND. Следовательно, S = R = 0 или S = R = 1, эти входные условия никогда не появятся. Эту проблему можно избежать с помощью условий SR = 00 и SR = 1.

Блок-схема

Принципиальная электрическая схема

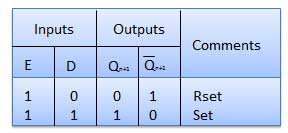

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | E = 0 |

Защелка отключена. Следовательно, никаких изменений в выходе. |

| 2 | E = 1 и D = 0 |

Если E = 1 и D = 0, то S = 0 и R = 1. Следовательно, независимо от текущего состояния, следующим состоянием является Q n + 1 = 0 и Q n + 1 bar = 1. Это условие сброса. |

| 3 | E = 1 и D = 1 |

Если E = 1 и D = 1, то S = 1 и R = 0. Это установит фиксатор и Q n + 1 = 1 и Q n + 1 бар = 0 независимо от текущего состояния. |

Защелка отключена. Следовательно, никаких изменений в выходе.

Если E = 1 и D = 0, то S = 0 и R = 1. Следовательно, независимо от текущего состояния, следующим состоянием является Q n + 1 = 0 и Q n + 1 bar = 1. Это условие сброса.

Если E = 1 и D = 1, то S = 1 и R = 0. Это установит фиксатор и Q n + 1 = 1 и Q n + 1 бар = 0 независимо от текущего состояния.

Toggle Flip Flop / T Flip Flop

Триггерный триггер — это в основном триггер JK с постоянно соединенными клеммами J и K. Он имеет только вход, обозначенный буквой T, как показано на диаграмме символов. Символ для триггера с положительным фронтом показан на блок-схеме.