Компьютерная логическая организация — обзор

В современном мире электроники термин « цифровой» обычно ассоциируется с компьютером, поскольку термин « цифровой» получен из того, как компьютеры выполняют операции путем подсчета цифр. На протяжении многих лет применение цифровой электроники было только в компьютерной системе. Но в настоящее время цифровая электроника используется во многих других приложениях. Ниже приведены некоторые примеры интенсивного использования цифровой электроники .

- Управление производственными процессами

- Военная система

- телевидение

- Система связи

- Медицинское оборудование

- радиолокационный

- навигация

Сигнал

Сигнал может быть определен как физическая величина, которая содержит некоторую информацию. Это функция одной или нескольких независимых переменных. Сигналы бывают двух типов.

- Аналоговый сигнал

- Цифровой сигнал

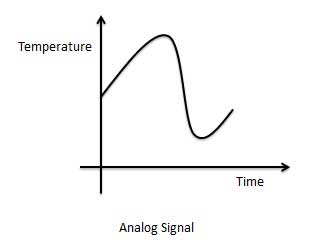

Аналоговый сигнал

Аналоговый сигнал определяется как сигнал, имеющий непрерывные значения. Аналоговый сигнал может иметь бесконечное количество разных значений. В сценарии реального мира большинство вещей, наблюдаемых в природе, являются аналоговыми. Примеры аналоговых сигналов следующие.

- температура

- давление

- Расстояние

- звук

- вольтаж

- Текущий

- Мощность

Графическое представление аналогового сигнала (температуры)

Схемы, которые обрабатывают аналоговые сигналы, называются аналоговыми схемами или системой. Примеры аналоговой системы следующие.

- Фильтр

- усилители

- Телевизионный приемник

- Регулятор скорости двигателя

Недостаток аналоговых систем

- Меньшая точность

- Меньше универсальности

- Больше шумового эффекта

- Больше искажений

- Больше влияния погоды

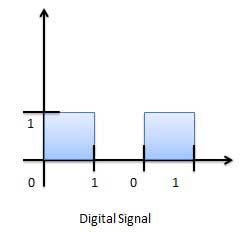

Цифровой сигнал

Цифровой сигнал определяется как сигнал, который имеет только конечное число различных значений. Цифровые сигналы не являются непрерывными сигналами. В цифровом электронном калькуляторе ввод осуществляется с помощью переключателей. Этот вход преобразуется в электрический сигнал, который имеет два дискретных значения или уровня. Один из них можно назвать низким уровнем, а другой называется высоким уровнем. Сигнал всегда будет одним из двух уровней. Этот тип сигнала называется цифровым сигналом. Примеры цифрового сигнала следующие.

- Двоичный сигнал

- Восьмеричный сигнал

- Шестнадцатеричный сигнал

Графическое представление цифрового сигнала (двоичный)

Цепи, которые обрабатывают цифровые сигналы, называются цифровыми системами или цифровыми цепями. Примеры цифровых систем следующие.

- Регистры

- Резкий поворот

- Счетчики

- Микропроцессоры

Преимущество цифровых систем

- Больше точности

- Больше универсальности

- Меньше искажений

- Легко общаться

- Возможное хранение информации

Сравнение аналогового и цифрового сигнала

| SN | Аналоговый сигнал | Цифровой сигнал |

|---|---|---|

| 1 | Аналоговый сигнал имеет бесконечные значения. | Цифровой сигнал имеет конечное число значений. |

| 2 | Аналоговый сигнал имеет непрерывный характер. | Цифровой сигнал имеет дискретную природу. |

| 3 | Аналоговый сигнал генерируется преобразователями и генераторами сигналов. | Цифровой сигнал генерируется аналого-цифровым преобразователем. |

| 4 | Пример аналогового сигнала — синусоида, треугольные волны. | Пример цифрового сигнала — двоичный сигнал. |

Цифровая система счисления

Цифровая система может понимать позиционную систему счисления только там, где есть несколько символов, называемых цифрами, и эти символы представляют разные значения в зависимости от положения, которое они занимают в номере.

Значение каждой цифры в номере можно определить с помощью

-

Цифра

-

Положение цифры в номере

-

База системы счисления (где база определяется как общее количество цифр, доступных в системе счисления).

Цифра

Положение цифры в номере

База системы счисления (где база определяется как общее количество цифр, доступных в системе счисления).

Десятичная система счисления

Система счисления, которую мы используем в нашей повседневной жизни, — это десятичная система счисления. У десятичной системы счисления есть основание 10, поскольку она использует 10 цифр от 0 до 9. В десятичной системе счисления последовательные позиции слева от десятичной точки представляют единицы, десятки, сотни, тысячи и так далее.

Каждая позиция представляет определенную силу основания (10). Например, десятичное число 1234 состоит из цифры 4 в позиции единиц, 3 в позиции десятков, 2 в позиции сотен и 1 в позиции тысяч, и его значение можно записать в виде

(1×1000) + (2×100) + (3×10) + (4×l) (1×10 3 ) + (2×10 2 ) + (3×10 1 ) + (4×l0 0 ) 1000 + 200 + 30 + 1 1234

Как программист или ИТ-специалист, вы должны понимать следующие системы счисления, которые часто используются в компьютерах.

| SN | Система счисления и описание |

|---|---|

| 1 | Двоичная система счисления

База 2. Используемые цифры: 0, 1 |

| 2 | Восьмеричная система счисления

База 8. Используемые цифры: от 0 до 7 |

| 3 | Гекса десятичная система счисления

База 16. Используемые цифры: от 0 до 9, используемые буквы: A- F |

База 2. Используемые цифры: 0, 1

База 8. Используемые цифры: от 0 до 7

База 16. Используемые цифры: от 0 до 9, используемые буквы: A- F

Двоичная система счисления

Характеристики

-

Использует две цифры, 0 и 1.

-

Также называется системой счисления Base 2

-

Каждая позиция в двоичном числе представляет степень 0 основания (2). Пример: 2 0

-

Последняя позиция в двоичном числе представляет собой степень x основания (2). Пример: 2 x, где x представляет последнюю позицию — 1.

Использует две цифры, 0 и 1.

Также называется системой счисления Base 2

Каждая позиция в двоичном числе представляет степень 0 основания (2). Пример: 2 0

Последняя позиция в двоичном числе представляет собой степень x основания (2). Пример: 2 x, где x представляет последнюю позицию — 1.

пример

Двоичный номер: 10101 2

Расчет десятичного эквивалента —

| шаг | Двоичный номер | Десятичное число |

|---|---|---|

| Шаг 1 | 10101 2 | ((1 × 2 4 ) + (0 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 )) 10 |

| Шаг 2 | 10101 2 | (16 + 0 + 4 + 0 + 1) 10 |

| Шаг 3 | 10101 2 | 21 10 |

Примечание: 10101 2 обычно записывается как 10101.

Восьмеричная система счисления

Характеристики

-

Использует восемь цифр, 0,1,2,3,4,5,6,7.

-

Также называется системой счисления Base 8

-

Каждая позиция в восьмеричном числе представляет степень 0 основания (8). Пример: 8 0

-

Последняя позиция в восьмеричном числе представляет собой степень x основания (8). Пример: 8 x, где x представляет последнюю позицию — 1.

Использует восемь цифр, 0,1,2,3,4,5,6,7.

Также называется системой счисления Base 8

Каждая позиция в восьмеричном числе представляет степень 0 основания (8). Пример: 8 0

Последняя позиция в восьмеричном числе представляет собой степень x основания (8). Пример: 8 x, где x представляет последнюю позицию — 1.

пример

Восьмеричное число — 12570 8

Расчет десятичного эквивалента —

| шаг | Восьмеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 12570 8 | ((1 × 8 4 ) + (2 × 8 3 ) + (5 × 8 2 ) + (7 × 8 1 ) + (0 × 8 0 )) 10 |

| Шаг 2 | 12570 8 | (4096 + 1024 + 320 + 56 + 0) 10 |

| Шаг 3 | 12570 8 | 5496 10 |

Примечание: 12570 8 обычно записывается как 12570.

Шестнадцатеричная система счисления

Характеристики

-

Использует 10 цифр и 6 букв, 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F.

-

Буквами обозначены числа, начинающиеся с 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

-

Также называется базовой 16-ти числовой системой.

-

Каждая позиция в шестнадцатеричном числе представляет степень 0 основания (16). Пример 16 0 .

-

Последняя позиция в шестнадцатеричном числе представляет собой степень x основания (16). Пример 16 x, где x представляет последнюю позицию — 1.

Использует 10 цифр и 6 букв, 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F.

Буквами обозначены числа, начинающиеся с 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

Также называется базовой 16-ти числовой системой.

Каждая позиция в шестнадцатеричном числе представляет степень 0 основания (16). Пример 16 0 .

Последняя позиция в шестнадцатеричном числе представляет собой степень x основания (16). Пример 16 x, где x представляет последнюю позицию — 1.

Пример —

Шестнадцатеричное число: 19FDE 16

Расчет десятичного эквивалента —

| шаг | Шестнадцатеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (F × 16 2 ) + (D × 16 1 ) + (E × 16 0 )) 10 |

| Шаг 2 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (15 × 16 2 ) + (13 × 16 1 ) + (14 × 16 0 )) 10 |

| Шаг 3 | 19FDE 16 | (65536 + 36864 + 3840 + 208 + 14) 10 |

| Шаг 4 | 19FDE 16 | 106462 10 |

Примечание. 19FDE 16 обычно записывается как 19FDE.

Преобразование системы счисления

Существует много методов или приемов, которые можно использовать для преобразования чисел из одной базы в другую. Мы продемонстрируем здесь следующее —

- Десятичное в другую базовую систему

- Другая базовая система в десятичном виде

- Другие базовые системы в недесятичные

- Сокращенный метод — от двоичного к октальному

- Сокращенный метод — Octal to Binary

- Сокращенный метод — от двоичного к шестнадцатеричному

- Сокращенный метод — от шестнадцатеричного до двоичного

Десятичное в другую базовую систему

меры

-

Шаг 1 — Разделите десятичное число для преобразования на значение новой базы.

-

Шаг 2 — Получить остаток от шага 1 как крайнюю правую цифру (наименее значимая цифра) нового базового номера.

-

Шаг 3 — Разделите частное от предыдущего деления на новую базу.

-

Шаг 4 — Запишите остаток от шага 3 в качестве следующей цифры (слева) от нового базового номера.

Шаг 1 — Разделите десятичное число для преобразования на значение новой базы.

Шаг 2 — Получить остаток от шага 1 как крайнюю правую цифру (наименее значимая цифра) нового базового номера.

Шаг 3 — Разделите частное от предыдущего деления на новую базу.

Шаг 4 — Запишите остаток от шага 3 в качестве следующей цифры (слева) от нового базового номера.

Повторите шаги 3 и 4, получая остатки справа налево, пока частное не станет равным нулю на шаге 3.

Последним полученным остатком будет Самая значимая цифра (MSD) нового базового номера.

Пример —

Десятичное число: 29 10

Расчет двоичного эквивалента —

| шаг | операция | Результат | остаток |

|---|---|---|---|

| Шаг 1 | 29/2 | 14 | 1 |

| Шаг 2 | 14/2 | 7 | 0 |

| Шаг 3 | 7/2 | 3 | 1 |

| Шаг 4 | 3/2 | 1 | 1 |

| Шаг 5 | 1/2 | 0 | 1 |

Как упоминалось в шагах 2 и 4, остатки должны быть расположены в обратном порядке, чтобы первый остаток стал наименьшей значащей цифрой (LSD), а последний остаток стал самой значимой цифрой (MSD).

Десятичное число — 29 10 = двоичное число — 11101 2 .

Другая базовая система в десятичную систему

меры

-

Шаг 1 — Определите столбцовое (позиционное) значение каждой цифры (это зависит от положения цифры и основания системы счисления).

-

Шаг 2 — Умножьте полученные значения столбцов (на шаге 1) на цифры в соответствующих столбцах.

-

Шаг 3 — Сумма продуктов, рассчитанных на шаге 2. Итоговое значение является десятичным значением.

Шаг 1 — Определите столбцовое (позиционное) значение каждой цифры (это зависит от положения цифры и основания системы счисления).

Шаг 2 — Умножьте полученные значения столбцов (на шаге 1) на цифры в соответствующих столбцах.

Шаг 3 — Сумма продуктов, рассчитанных на шаге 2. Итоговое значение является десятичным значением.

пример

Двоичный номер — 11101 2

Расчет десятичного эквивалента —

| шаг | Двоичный номер | Десятичное число |

|---|---|---|

| Шаг 1 | 11101 2 | ((1 × 2 4 ) + (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 )) 10 |

| Шаг 2 | 11101 2 | (16 + 8 + 4 + 0 + 1) 10 |

| Шаг 3 | 11101 2 | 29 10 |

Двоичный номер — 11101 2 = Десятичное число — 29 10

Другая базовая система в недесятичной системе

меры

-

Шаг 1 — Преобразование исходного числа в десятичное число (основание 10).

-

Шаг 2 — Преобразуйте полученное десятичное число в новое базовое число.

Шаг 1 — Преобразование исходного числа в десятичное число (основание 10).

Шаг 2 — Преобразуйте полученное десятичное число в новое базовое число.

пример

Восьмеричное число — 25 8

Расчет двоичного эквивалента —

Шаг 1 — конвертировать в десятичную

| шаг | Восьмеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 25 8 | ((2 × 8 1 ) + (5 × 8 0 )) 10 |

| Шаг 2 | 25 8 | (16 + 5) 10 |

| Шаг 3 | 25 8 | 21 10 |

Восьмеричное число — 25 8 = Десятичное число — 21 10

Шаг 2 — Преобразование десятичного числа в двоичное

| шаг | операция | Результат | остаток |

|---|---|---|---|

| Шаг 1 | 21/2 | 10 | 1 |

| Шаг 2 | 10/2 | 5 | 0 |

| Шаг 3 | 5/2 | 2 | 1 |

| Шаг 4 | 2/2 | 1 | 0 |

| Шаг 5 | 1/2 | 0 | 1 |

Десятичное число — 21 10 = двоичное число — 10101 2

Восьмеричное число — 25 8 = двоичное число — 10101 2

Сокращенный метод — от двоичного к октальному

меры

-

Шаг 1 — Разделите двоичные цифры на группы по три (начиная справа).

-

Шаг 2 — Преобразуйте каждую группу из трех двоичных цифр в одну восьмеричную цифру.

Шаг 1 — Разделите двоичные цифры на группы по три (начиная справа).

Шаг 2 — Преобразуйте каждую группу из трех двоичных цифр в одну восьмеричную цифру.

пример

Двоичный номер — 10101 2

Вычисление Восьмеричного Эквивалента —

| шаг | Двоичный номер | Восьмеричное число |

|---|---|---|

| Шаг 1 | 10101 2 | 010 101 |

| Шаг 2 | 10101 2 | 2 8 5 8 |

| Шаг 3 | 10101 2 | 25 8 |

Двоичный номер — 10101 2 = Восьмеричное число — 25 8

Сокращенный метод — Octal to Binary

меры

-

Шаг 1 — Преобразуйте каждую восьмеричную цифру в трехзначное двоичное число (восьмеричные цифры могут рассматриваться как десятичные для этого преобразования).

-

Шаг 2 — Объедините все получившиеся двоичные группы (по 3 цифры в каждой) в одно двоичное число.

Шаг 1 — Преобразуйте каждую восьмеричную цифру в трехзначное двоичное число (восьмеричные цифры могут рассматриваться как десятичные для этого преобразования).

Шаг 2 — Объедините все получившиеся двоичные группы (по 3 цифры в каждой) в одно двоичное число.

пример

Восьмеричное число — 25 8

Расчет двоичного эквивалента —

| шаг | Восьмеричное число | Двоичный номер |

|---|---|---|

| Шаг 1 | 25 8 | 2 10 5 10 |

| Шаг 2 | 25 8 | 010 2 101 2 |

| Шаг 3 | 25 8 | 010101 2 |

Восьмеричное число — 25 8 = двоичное число — 10101 2

Сокращенный метод — от двоичного к шестнадцатеричному

меры

-

Шаг 1 — Разделите двоичные цифры на группы по четыре (начиная справа).

-

Шаг 2 — Преобразуйте каждую группу из четырех двоичных цифр в один шестнадцатеричный символ.

Шаг 1 — Разделите двоичные цифры на группы по четыре (начиная справа).

Шаг 2 — Преобразуйте каждую группу из четырех двоичных цифр в один шестнадцатеричный символ.

пример

Двоичный номер — 10101 2

Расчет шестнадцатеричного эквивалента —

| шаг | Двоичный номер | Шестнадцатеричное число |

|---|---|---|

| Шаг 1 | 10101 2 | 0001 0101 |

| Шаг 2 | 10101 2 | 1 10 5 10 |

| Шаг 3 | 10101 2 | 15 16 |

Двоичный номер — 10101 2 = шестнадцатеричное число — 15 16

Сокращенный метод — от шестнадцатеричного до двоичного

меры

-

Шаг 1 — Преобразуйте каждую шестнадцатеричную цифру в четырехзначное двоичное число (шестнадцатеричные цифры могут рассматриваться как десятичные для этого преобразования).

-

Шаг 2 — Объедините все получившиеся двоичные группы (по 4 цифры в каждой) в одно двоичное число.

Шаг 1 — Преобразуйте каждую шестнадцатеричную цифру в четырехзначное двоичное число (шестнадцатеричные цифры могут рассматриваться как десятичные для этого преобразования).

Шаг 2 — Объедините все получившиеся двоичные группы (по 4 цифры в каждой) в одно двоичное число.

пример

Шестнадцатеричное число — 15 16

Расчет двоичного эквивалента —

| шаг | Шестнадцатеричное число | Двоичный номер |

|---|---|---|

| Шаг 1 | 15 16 | 1 10 5 10 |

| Шаг 2 | 15 16 | 0001 2 0101 2 |

| Шаг 3 | 15 16 | 00010101 2 |

Шестнадцатеричное число — 15 16 = двоичное число — 10101 2

Двоичные коды

В кодировании, когда числа, буквы или слова представлены определенной группой символов, говорят, что число, буква или слово кодируются. Группа символов называется кодом. Цифровые данные представляются, хранятся и передаются в виде группы двоичных битов. Эта группа также называется двоичным кодом . Двоичный код представлен числом, а также буквенно-цифровой буквой.

Преимущества двоичного кода

Ниже приведен список преимуществ, которые предлагает двоичный код.

-

Двоичные коды подходят для компьютерных приложений.

-

Двоичные коды подходят для цифровой связи.

-

Двоичные коды делают анализ и проектирование цифровых схем, если мы используем двоичные коды.

-

Поскольку используются только 0 и 1, реализация становится легкой.

Двоичные коды подходят для компьютерных приложений.

Двоичные коды подходят для цифровой связи.

Двоичные коды делают анализ и проектирование цифровых схем, если мы используем двоичные коды.

Поскольку используются только 0 и 1, реализация становится легкой.

Классификация двоичных кодов

Коды широко подразделяются на следующие четыре категории.

- Взвешенные коды

- Невзвешенные коды

- Двоичный код десятичного кода

- Буквенно-цифровые коды

- Коды обнаружения ошибок

- Коды, исправляющие ошибки

Взвешенные коды

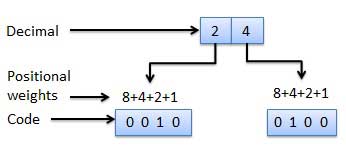

Взвешенные двоичные коды — это те двоичные коды, которые подчиняются принципу позиционного веса. Каждая позиция числа представляет определенный вес. Несколько систем кодов используются для выражения десятичных цифр от 0 до 9. В этих кодах каждая десятичная цифра представлена группой из четырех битов.

Невзвешенные коды

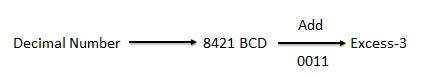

В этом типе двоичных кодов позиционные веса не назначаются. Примерами невзвешенных кодов являются код Excess-3 и код Грея.

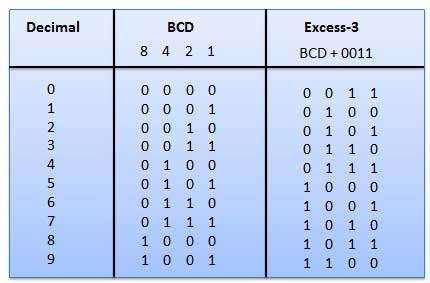

Код избытка-3

Код Excess-3 также называется кодом XS-3. Это невзвешенный код, используемый для выражения десятичных чисел. Кодовые слова Excess-3 получаются из кодовых слов BCD 8421, добавляющих (0011) 2 или (3) 10 к каждому кодовому слову в 8421. Коды избыточного 3 получают следующим образом:

пример

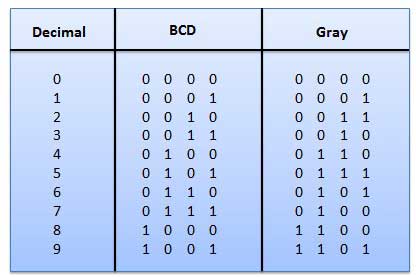

Серый код

Это невзвешенный код и это не арифметические коды. Это означает, что для битовой позиции нет конкретных весов. У него есть особая особенность, что при каждом увеличении десятичного числа будет изменяться только один бит, как показано на рис. Поскольку за один раз изменяется только один бит, серый код называется единичным кодом расстояния. Серый код — это циклический код. Код Грея нельзя использовать для арифметической операции.

Применение кода Грея

-

Серый код широко используется в датчиках положения вала.

-

Датчик положения вала создает кодовое слово, которое представляет угловое положение вала.

Серый код широко используется в датчиках положения вала.

Датчик положения вала создает кодовое слово, которое представляет угловое положение вала.

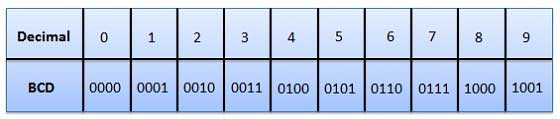

Двоичный код (BCD)

В этом коде каждая десятичная цифра представлена 4-битным двоичным числом. BCD — это способ выразить каждую десятичную цифру двоичным кодом. В BCD с четырьмя битами мы можем представить шестнадцать чисел (от 0000 до 1111). Но в коде BCD используются только первые десять из них (от 0000 до 1001). Остальные шесть кодовых комбинаций, то есть 1010–1111, недопустимы в BCD.

Преимущества кодов BCD

- Это очень похоже на десятичную систему.

- Нам нужно запомнить двоичный эквивалент десятичных чисел только от 0 до 9.

Недостатки кодов BCD

-

Сложение и вычитание BCD имеют разные правила.

-

Арифметика BCD немного сложнее.

-

BCD требуется большее количество бит, чем двоичное, чтобы представить десятичное число. Так что BCD менее эффективен, чем двоичный.

Сложение и вычитание BCD имеют разные правила.

Арифметика BCD немного сложнее.

BCD требуется большее количество бит, чем двоичное, чтобы представить десятичное число. Так что BCD менее эффективен, чем двоичный.

Буквенно-цифровые коды

Бинарная цифра или бит может представлять только два символа, поскольку имеет только два состояния: «0» или «1». Но этого недостаточно для связи между двумя компьютерами, потому что там нам нужно гораздо больше символов для связи. Эти символы должны представлять 26 алфавитов с заглавными и строчными буквами, числами от 0 до 9, знаками препинания и другими символами.

Буквенно-цифровые коды представляют собой коды, которые представляют цифры и буквенные символы. В основном такие коды также представляют другие символы, такие как символы и различные инструкции, необходимые для передачи информации. Буквенно-цифровой код должен содержать не менее 10 цифр и 26 букв алфавита, т.е. всего 36 знаков. Следующие три буквенно-цифровых кода очень часто используются для представления данных.

- Американский стандартный код для обмена информацией (ASCII).

- Расширенный двоичный код десятичного кода обмена (EBCDIC).

- Пяти битный код Бодо.

Код ASCII — это 7-битный код, тогда как EBCDIC — это 8-битный код. Код ASCII чаще используется во всем мире, в то время как EBCDIC используется в основном на больших компьютерах IBM.

Коды ошибок

Существуют методы двоичного кода, позволяющие обнаруживать и исправлять данные во время передачи данных.

| Код ошибки | Описание |

|---|---|

| Методы обнаружения и исправления ошибок |

Обнаружение и исправление ошибок

Преобразование кодов

Существует много методов или приемов, которые можно использовать для преобразования кода из одного формата в другой. Мы продемонстрируем здесь следующее

- Двоичное преобразование в BCD

- BCD в двоичное преобразование

- BCD для Excess-3

- Избыток-3 в BCD

Двоичное преобразование в BCD

меры

-

Шаг 1 — Преобразование двоичного числа в десятичное.

-

Шаг 2 — Преобразование десятичного числа в BCD.

Шаг 1 — Преобразование двоичного числа в десятичное.

Шаг 2 — Преобразование десятичного числа в BCD.

Пример — конвертировать (11101) 2 в BCD.

Шаг 1 — конвертировать в десятичную

Двоичный номер — 11101 2

Расчет десятичного эквивалента —

| шаг | Двоичный номер | Десятичное число |

|---|---|---|

| Шаг 1 | 11101 2 | ((1 × 2 4 ) + (1 × 2 3 ) + (1 × 2 2 ) + (0 × 2 1 ) + (1 × 2 0 )) 10 |

| Шаг 2 | 11101 2 | (16 + 8 + 4 + 0 + 1) 10 |

| Шаг 3 | 11101 2 | 29 10 |

Двоичный номер — 11101 2 = Десятичное число — 29 10

Шаг 2 — конвертировать в BCD

Десятичное число — 29 10

Расчет BCD-эквивалента. Преобразуйте каждую цифру в группы из четырех двоичных цифр.

| шаг | Десятичное число | преобразование |

|---|---|---|

| Шаг 1 | 29 10 | 0010 2 1001 2 |

| Шаг 2 | 29 10 | 00101001 BCD |

Результат

(11101) 2 = (00101001) BCD

BCD в двоичное преобразование

меры

-

Шаг 1 — Преобразуйте число BCD в десятичное.

-

Шаг 2 — Преобразование десятичного числа в двоичное.

Шаг 1 — Преобразуйте число BCD в десятичное.

Шаг 2 — Преобразование десятичного числа в двоичное.

Пример — конвертировать (00101001) BCD в двоичный файл.

Шаг 1 — конвертировать в BCD

Номер BCD — (00101001) BCD

Расчет десятичного эквивалента. Преобразуйте каждые четыре цифры в группу и получите десятичный эквивалент для каждой группы.

| шаг | Номер BCD | преобразование |

|---|---|---|

| Шаг 1 | (00101001) BCD | 0010 2 1001 2 |

| Шаг 2 | (00101001) BCD | 2 10 9 10 |

| Шаг 3 | (00101001) BCD | 29 10 |

BCD номер — (00101001) BCD = десятичное число — 29 10

Шаг 2 — Преобразовать в двоичный

Использовал метод длинного деления для преобразования в десятичную систему в двоичную.

Десятичное число — 29 10

Расчет двоичного эквивалента —

| шаг | операция | Результат | остаток |

|---|---|---|---|

| Шаг 1 | 29/2 | 14 | 1 |

| Шаг 2 | 14/2 | 7 | 0 |

| Шаг 3 | 7/2 | 3 | 1 |

| Шаг 4 | 3/2 | 1 | 1 |

| Шаг 5 | 1/2 | 0 | 1 |

Как упомянуто в шагах 2 и 4, остатки должны быть расположены в обратном порядке, чтобы первый остаток стал младшей цифрой (LSD), а последний остаток стал самой старшей цифрой (MSD).

Десятичное число — 29 10 = двоичное число — 11101 2

Результат

(00101001) BCD = (11101) 2

BCD для Excess-3

меры

-

Шаг 1 — Преобразование BCD в десятичную.

-

Шаг 2 — Добавьте (3) 10 к этому десятичному числу.

-

Шаг 3 — Преобразование в двоичный файл, чтобы получить избыточный код 3.

Шаг 1 — Преобразование BCD в десятичную.

Шаг 2 — Добавьте (3) 10 к этому десятичному числу.

Шаг 3 — Преобразование в двоичный файл, чтобы получить избыточный код 3.

Пример — конвертировать (1001) BCD в Excess-3.

Шаг 1 — конвертировать в десятичную

(1001) BCD = 9 10

Шаг 2 — Добавьте 3 к десятичной

(9) 10 + (3) 10 = (12) 10

Шаг 3 — Преобразование в Избыток-3

(12) 10 = (1100) 2

Результат

(1001) BCD = (1100) XS-3

Превышение 3 для преобразования BCD

меры

-

Шаг 1 — Вычтите (0011) 2 из каждых 4 битов избыточной цифры 3, чтобы получить соответствующий код BCD.

Шаг 1 — Вычтите (0011) 2 из каждых 4 битов избыточной цифры 3, чтобы получить соответствующий код BCD.

Пример — конвертировать (10011010) XS-3 в BCD.

Given XS-3 number = 1 0 0 1 1 0 1 0

Subtract (0011) 2 = 1 0 0 1 0 1 1 1

--------------------

BCD = 0 1 1 0 0 1 1 1

Результат

(10011010) XS-3 = (01100111) BCD

Дополнить арифметику

Дополнения используются в цифровых компьютерах для упрощения операции вычитания и для логических манипуляций. Для каждой системы radix-r (основание системы счисления r представляет собой) существует два типа дополнений.

| SN | комплемент | Описание |

|---|---|---|

| 1 | Radix Complement | Основное дополнение называется дополнением r |

| 2 | Уменьшенный Radix Complement | Уменьшенное радикальное дополнение называется дополнением (r-1) |

Бинарная система дополняет

Поскольку двоичная система имеет базу r = 2. Таким образом, два типа дополнений для двоичной системы — это дополнение 2 и дополнение 1.

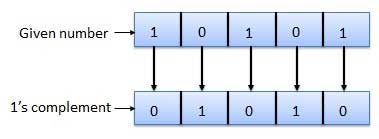

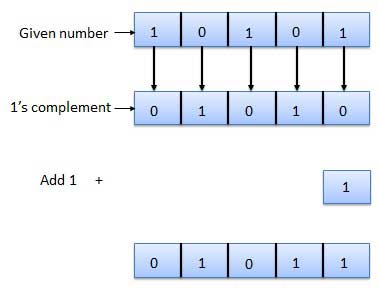

1 дополнение

Дополнение числа 1 определяется путем изменения всех 1 на 0 и всех 0 на 1. Это называется принятием дополнения или дополнением 1. Пример дополнения 1 следующий.

2 дополнения

Дополнение двоичного числа к 2 получается добавлением 1 к младшему значащему биту (LSB) дополнения к числу 1.

Дополнение 2 = дополнение 1 + 1

Пример дополнения 2 заключается в следующем.

Двоичная арифметика

Двоичная арифметика является неотъемлемой частью всех цифровых компьютеров и многих других цифровых систем.

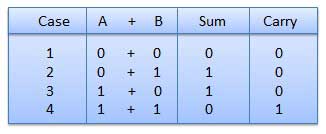

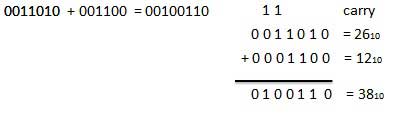

Двоичное дополнение

Это ключ для двоичного вычитания, умножения, деления. Есть четыре правила двоичного сложения.

В четвертом случае двоичное сложение создает сумму (1 + 1 = 10), то есть 0 записывается в данный столбец и переносит 1 в следующий столбец.

Пример — дополнение

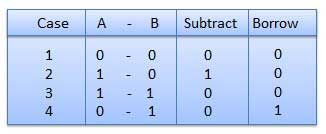

Двоичное вычитание

Вычитание и заимствование , эти два слова будут очень часто использоваться для двоичного вычитания. Есть четыре правила двоичного вычитания.

Пример — вычитание

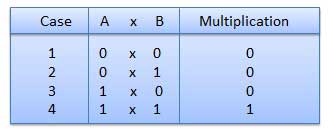

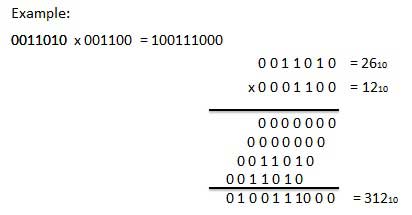

Двоичное Умножение

Двоичное умножение аналогично десятичному умножению. Это проще, чем десятичное умножение, потому что участвуют только 0 и 1. Есть четыре правила двоичного умножения.

Пример — Умножение

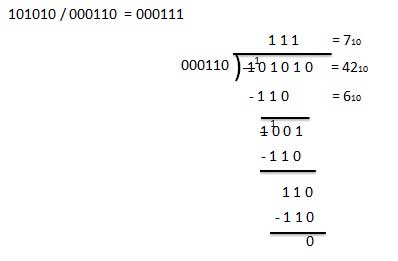

Бинарный отдел

Бинарное деление похоже на десятичное деление. Это называется длинной процедурой деления.

Пример — Разделение

Восьмеричная арифметика

Восьмеричная система счисления

Ниже приведены характеристики восьмеричной системы счисления.

-

Использует восемь цифр, 0,1,2,3,4,5,6,7.

-

Также называется системой счисления Base 8.

-

Каждая позиция в восьмеричном числе представляет степень 0 основания (8). Пример: 8 0

-

Последняя позиция в восьмеричном числе представляет собой степень x основания (8). Пример: 8 x, где x представляет последнюю позицию — 1.

Использует восемь цифр, 0,1,2,3,4,5,6,7.

Также называется системой счисления Base 8.

Каждая позиция в восьмеричном числе представляет степень 0 основания (8). Пример: 8 0

Последняя позиция в восьмеричном числе представляет собой степень x основания (8). Пример: 8 x, где x представляет последнюю позицию — 1.

пример

Восьмеричное число — 12570 8

Расчет десятичного эквивалента —

| шаг | Восьмеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 12570 8 | ((1 × 8 4 ) + (2 × 8 3 ) + (5 × 8 2 ) + (7 × 8 1 ) + (0 × 8 0 )) 10 |

| Шаг 2 | 12570 8 | (4096 + 1024 + 320 + 56 + 0) 10 |

| Шаг 3 | 12570 8 | 5496 10 |

Примечание — 12570 8 обычно записывается как 12570.

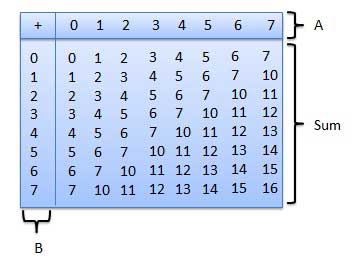

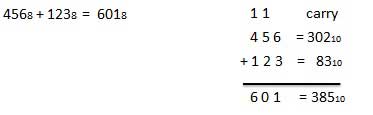

Восьмеричное сложение

Следующая таблица восьмеричного сложения поможет вам справиться с восьмеричным сложением.

Чтобы использовать эту таблицу, просто следуйте указаниям, используемым в этом примере: Добавьте 6 8 и 5 8 . Найдите 6 в столбце A, затем найдите 5 в столбце B. Точка в области «сумма», где эти два столбца пересекаются, является «суммой» двух чисел.

6 8 + 5 8 = 13 8 .

Пример — дополнение

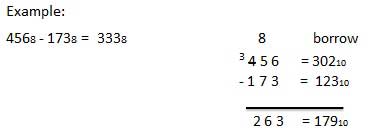

Восьмеричное вычитание

Вычитание восьмеричных чисел следует тем же правилам, что и вычитание чисел в любой другой системе счисления. Единственное изменение в заемном номере. В десятичной системе вы берете группу из 10 10 . В двоичной системе вы берете группу из 2 10 . В восьмеричной системе вы занимаетесь группой из 8 10 .

Пример — вычитание

Шестнадцатеричная арифметика

Шестнадцатеричная система счисления

Ниже приведены характеристики шестнадцатеричной системы счисления.

-

Использует 10 цифр и 6 букв, 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F.

-

Буквами обозначены числа, начинающиеся с 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

-

Также называется базовой 16-ти числовой системой.

-

Каждая позиция в шестнадцатеричном числе представляет степень 0 основания (16). Пример — 16 0

-

Последняя позиция в шестнадцатеричном числе представляет собой степень x основания (16). Пример — 16 x, где x представляет последнюю позицию — 1.

Использует 10 цифр и 6 букв, 0,1,2,3,4,5,6,7,8,9, A, B, C, D, E, F.

Буквами обозначены числа, начинающиеся с 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

Также называется базовой 16-ти числовой системой.

Каждая позиция в шестнадцатеричном числе представляет степень 0 основания (16). Пример — 16 0

Последняя позиция в шестнадцатеричном числе представляет собой степень x основания (16). Пример — 16 x, где x представляет последнюю позицию — 1.

пример

Шестнадцатеричное число — 19FDE 16

Расчет десятичного эквивалента —

| шаг | Шестнадцатеричное число | Десятичное число |

|---|---|---|

| Шаг 1 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (F × 16 2 ) + (D × 16 1 ) + (E × 16 0 )) 10 |

| Шаг 2 | 19FDE 16 | ((1 × 16 4 ) + (9 × 16 3 ) + (15 × 16 2 ) + (13 × 16 1 ) + (14 × 16 0 )) 10 |

| Шаг 3 | 19FDE 16 | (65536 + 36864 + 3840 + 208 + 14) 10 |

| Шаг 4 | 19FDE 16 | 106462 10 |

Примечание. 19FDE 16 обычно записывается как 19FDE.

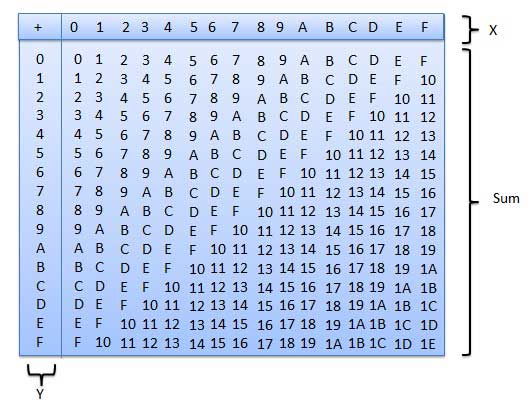

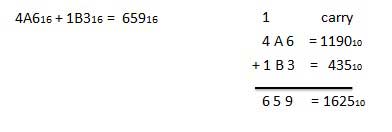

Шестнадцатеричное дополнение

Следующая таблица шестнадцатеричного сложения очень поможет вам справиться с шестнадцатеричным сложением.

Чтобы использовать эту таблицу, просто следуйте указаниям, используемым в этом примере — Добавьте A 16 и 5 16 . Найдите A в столбце X, затем найдите 5 в столбце Y. Точка в области «сумма», где эти два столбца пересекаются, является суммой двух чисел.

A 16 + 5 16 = F 16 .

Пример — дополнение

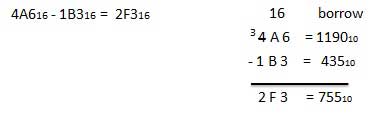

Шестнадцатеричное вычитание

Вычитание шестнадцатеричных чисел следует тем же правилам, что и вычитание чисел в любой другой системе счисления. Единственное изменение в заемном номере. В десятичной системе вы берете группу из 10 10 . В двоичной системе вы берете группу из 2 10 . В шестнадцатеричной системе вы заимствуете группу из 16 10 .

Пример — вычитание

Булева алгебра

Булева алгебра используется для анализа и упрощения цифровых (логических) схем. Он использует только двоичные числа, то есть 0 и 1. Он также называется двоичной алгеброй или логической алгеброй . Булева алгебра была изобретена Джорджем Булем в 1854 году.

Правило в булевой алгебре

Ниже приведены важные правила, используемые в булевой алгебре.

-

Используемая переменная может иметь только два значения. Двоичный 1 для высокого и двоичный 0 для низкого.

-

Дополнение к переменной представлено надстрочной точкой (-). Таким образом, дополнение переменной B представляется как

, Таким образом, если B = 0, то

= 1 и B = 1 тогда

= 0

-

ORing переменных представлен знаком плюс (+) между ними. Например, OR для A, B, C представлен как A + B + C.

-

Логическое И для двух или более переменных представляется записью точки между ними, такой как ABC. Иногда точка может быть опущена, как ABC.

Используемая переменная может иметь только два значения. Двоичный 1 для высокого и двоичный 0 для низкого.

Дополнение к переменной представлено надстрочной точкой (-). Таким образом, дополнение переменной B представляется как

ORing переменных представлен знаком плюс (+) между ними. Например, OR для A, B, C представлен как A + B + C.

Логическое И для двух или более переменных представляется записью точки между ними, такой как ABC. Иногда точка может быть опущена, как ABC.

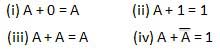

Булевы законы

Существует шесть типов булевых законов.

Коммутативное право

Любая двоичная операция, которая удовлетворяет следующему выражению, называется коммутативной операцией.

Коммутативный закон гласит, что изменение последовательности переменных не влияет на выход логической схемы.

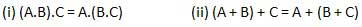

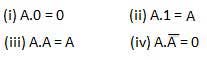

Ассоциативный закон

Этот закон гласит, что порядок, в котором выполняются логические операции, не имеет значения, поскольку их эффект одинаков.

Распределительное право

Дистрибутивное право устанавливает следующее условие.

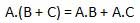

И закон

Эти законы используют операцию AND. Поэтому они называются законами И.

ИЛИ закон

Эти законы используют операцию ИЛИ. Поэтому они называются законами ИЛИ .

Закон об обращении

Этот закон использует операцию НЕ. Закон обращения гласит, что двойная инверсия переменной приводит к самой исходной переменной.

Важные булевы теоремы

Ниже приведены несколько важных булевых теорем.

| Булева функция / теоремы | Описание |

|---|---|

| Булевы функции и выражения, реализация K-Map и NAND Gates | |

| Теорема де Моргана 1 и теорема 2 |

Логические ворота

Логические элементы являются основными строительными блоками любой цифровой системы. Это электронная схема, имеющая один или несколько входов и только один выход. Связь между входом и выходом основана на определенной логике . Исходя из этого, логические логические элементы называются логическим элементом И, ИЛИ, НЕ ИЛИ

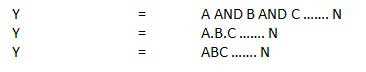

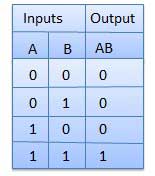

И Ворота

Схема, которая выполняет операцию И, показана на рисунке. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

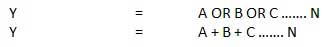

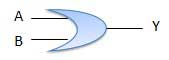

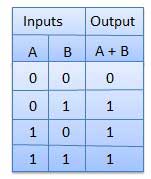

ИЛИ Ворота

Схема, которая выполняет операцию ИЛИ, показана на рисунке. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

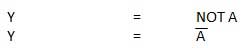

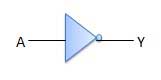

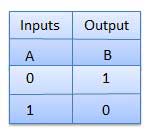

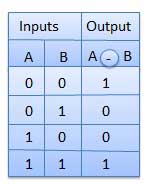

НЕ Ворота

НЕ Ворота также известен как Инвертор . Он имеет один вход A и один выход Y.

Логическая схема

Таблица правды

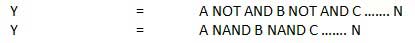

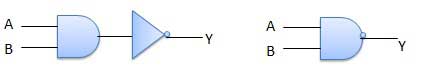

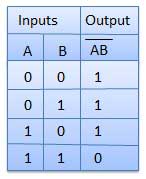

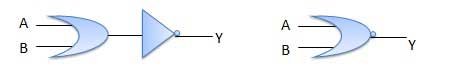

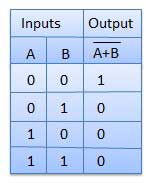

NAND Gate

Операция NOT-AND известна как операция NAND. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

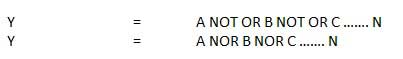

NOR Gate

Операция NOT-OR называется операцией NOR. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

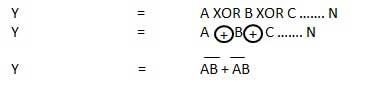

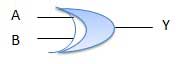

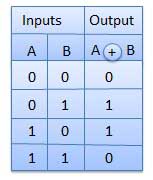

XOR Gate

Ворота XOR или Ex-OR — это особый тип ворот. Он может быть использован в половинном сумматоре, полном сумматоре и вычитателе. Вентиль с исключительным ИЛИ сокращается как вентиль EX-ИЛИ или иногда как вентиль Х-ИЛИ. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

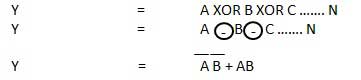

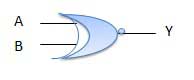

Ворота XNOR

Ворота XNOR — это особый тип ворот. Он может быть использован в половинном сумматоре, полном сумматоре и вычитателе. Вентиль с эксклюзивным NOR сокращенно обозначается как вентиль EX-NOR или иногда как вентиль X-NOR. Он имеет n входов (n> = 2) и один выход.

Логическая схема

Таблица правды

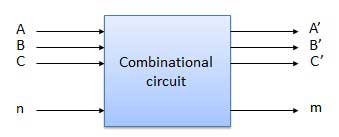

Комбинационные схемы

Комбинационная схема — это схема, в которой мы объединяем различные элементы схемы, например, кодер, декодер, мультиплексор и демультиплексор. Некоторые характеристики комбинационных схем следующие —

-

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

-

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

-

Комбинационная схема может иметь n входов и m выходов.

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

Комбинационная схема может иметь n входов и m выходов.

Блок-схема

Мы собираемся разработать несколько важных комбинационных схем следующим образом.

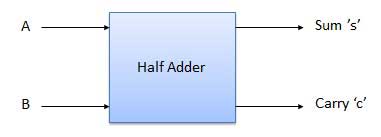

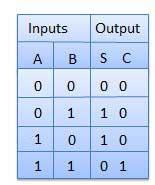

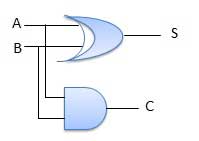

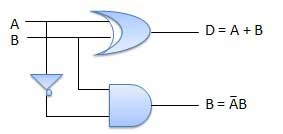

Полумесяц

Половина сумматора представляет собой комбинационную логическую схему с двумя входами и двумя выходами. Схема полусумметра предназначена для сложения двух однобитовых двоичных чисел A и B. Это базовый строительный блок для сложения двух однобитовых чисел. Эта схема имеет два выхода переноса и суммы .

Блок-схема

Таблица правды

Принципиальная электрическая схема

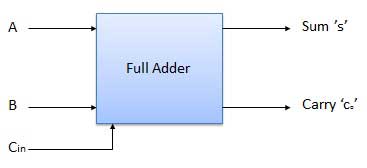

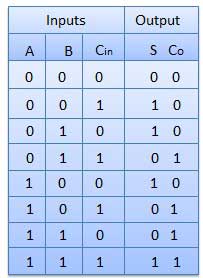

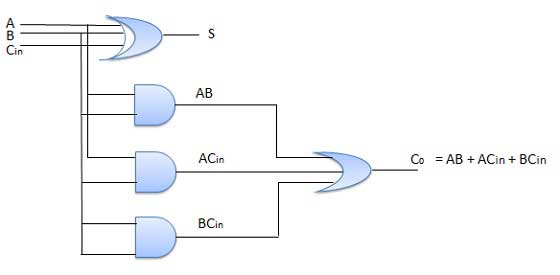

Полный сумматор

Полный сумматор разработан, чтобы преодолеть недостаток схемы Half Adder. Он может добавлять два однобитных числа A и B и переносить c. Полный сумматор представляет собой комбинацию из трех входов и двух выходов.

Блок-схема

Таблица правды

Принципиальная электрическая схема

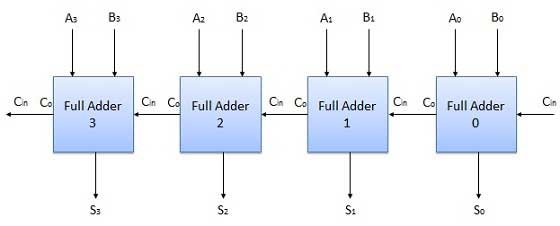

N-битный параллельный сумматор

Полный сумматор способен добавлять только два однозначных двоичных числа вместе с вводом переноса. Но на практике нам нужно добавить двоичные числа, которые намного длиннее одного бита. Чтобы добавить два n-битных двоичных числа, нам нужно использовать n-битный параллельный сумматор. Он использует несколько полных сумматоров в каскаде. Выход переноса предыдущего полного сумматора соединен с вводом переноса следующего полного сумматора.

4-битный параллельный сумматор

На блок-схеме A 0 и B 0 представляют младший бит четырехбитовых слов A и B. Следовательно, Full Adder-0 является самой низкой ступенью. Следовательно, его C in постоянно равен 0. Остальные соединения точно такие же, как у n-битного параллельного сумматора, показанного на рис. Четырехбитный параллельный сумматор — очень распространенная логическая схема.

Блок-схема

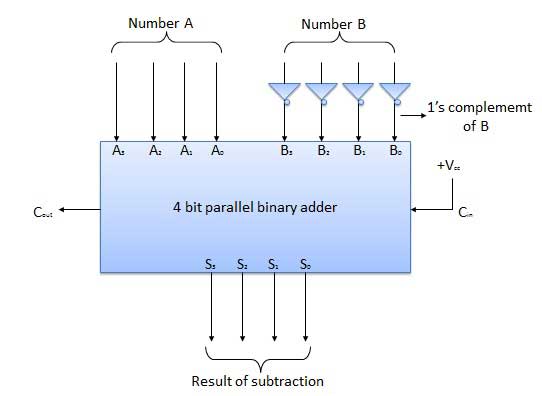

N-разрядный параллельный вычитатель

Вычитание можно выполнить, взяв 1 или 2 в дополнение к числу, которое должно быть вычтено. Например, мы можем выполнить вычитание (AB), добавив 1 или 2 в дополнение к B к A. Это означает, что мы можем использовать двоичный сумматор для выполнения двоичного вычитания.

4-битный параллельный вычитатель

Вычитаемое число (B) сначала пропускается через инверторы для получения дополнения к 1. Затем 4-разрядный сумматор добавляет A и 2 к B для вычитания. S 3 S 2 S 1 S 0 представляет результат двоичного вычитания (AB), а выходной сигнал C out представляет полярность результата. Если A> B, то Cout = 0 и результат двоичной формы (AB), тогда C out = 1, и результат находится в форме дополнения 2.

Блок-схема

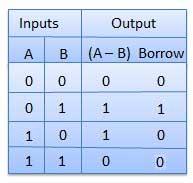

Половина вычитателей

Половина вычитателя представляет собой комбинированную схему с двумя входами и двумя выходами (разность и заем). Он выдает разницу между двумя двоичными битами на входе, а также выводит (заимствовать), чтобы указать, был ли заимствован 1. В вычитании (AB) A называется битом Minuend, а B называется битом Subtrahend.

Таблица правды

Принципиальная электрическая схема

Полные вычитатели

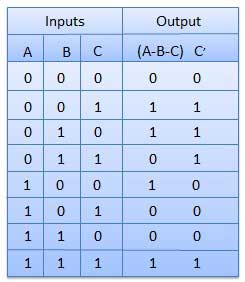

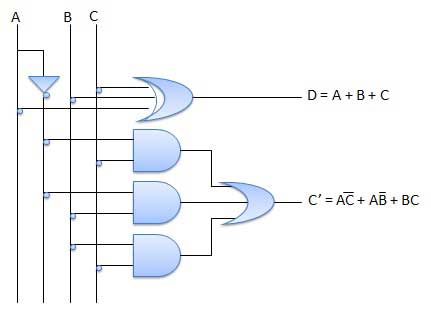

Недостаток половины вычитателя преодолевается полным вычитателем. Полный вычитатель представляет собой комбинационную схему с тремя входами A, B, C и двумя выходами D и C ‘. A — это «minuend», B — «вычитаемое», C — «заем», полученный на предыдущем этапе, D — это результат разницы, а C «- результат заимствования».

Таблица правды

Принципиальная электрическая схема

мультиплексоры

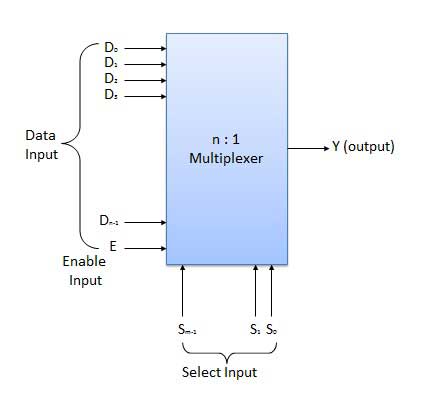

Мультиплексор — это особый тип комбинационной схемы. Есть n входов данных, один выход и m выбор входа с 2m = n. Это цифровая схема, которая выбирает один из n входов данных и направляет его на выход. Выбор одного из n входов осуществляется выбранными входами. В зависимости от цифрового кода, применяемого на выбранных входах, один из n источников данных выбирается и передается на один выход Y. E называется стробирующим или разрешающим входом, который полезен для каскадирования. Обычно это активный терминал низкого уровня, что означает, что он будет выполнять требуемую операцию, когда он низкий.

Блок-схема

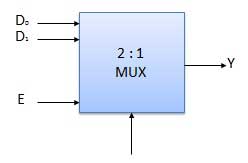

Мультиплексоры бывают разных вариантов

- Мультиплексор 2: 1

- Мультиплексор 4: 1

- Мультиплексор 16: 1

- Мультиплексор 32: 1

Блок-схема

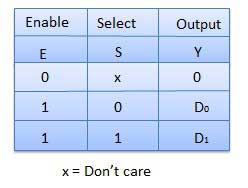

Таблица правды

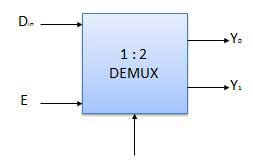

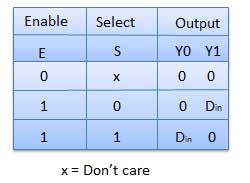

демультиплексоры

Демультиплексор выполняет обратную операцию мультиплексора, то есть он получает один вход и распределяет его по нескольким выходам. Он имеет только один вход, n выходов, m выбор входа. Одновременно выбирается только одна выходная строка, и вход передается на выбранную выходную строку. Демультиплексор эквивалентен однополюсному многоходовому переключателю, как показано на рис.

Демультиплексоры выпускаются в нескольких вариантах.

- Демультиплексор 1: 2

- Демультиплексор 1: 4

- Демультиплексор 1:16

- Демультиплексор 1:32

Блок-схема

Таблица правды

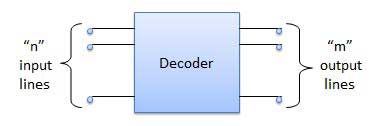

дешифратор

Декодер — комбинационная схема. Он имеет n входов и максимум m = 2n выходов. Декодер идентичен демультиплексору без ввода данных. Он выполняет операции, которые в точности противоположны кодировщику.

Блок-схема

Примеры декодеров следующие.

- Преобразователи кода

- BCD до семи сегментных декодеров

- Nixie ламповые декодеры

- Релейный привод

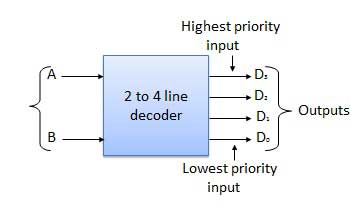

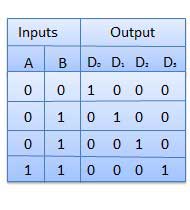

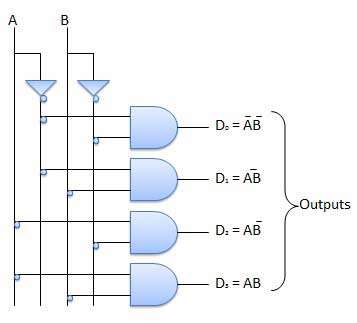

2 до 4-х строчный декодер

Блок-схема 2-4 линейного декодера показана на рис. A и B — два входа, где от D до D — четыре выхода. Таблица правды объясняет операции декодера. Это показывает, что каждый выход равен 1 только для определенной комбинации входов.

Блок-схема

Таблица правды

Логическая схема

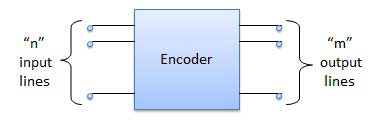

кодировщик

Энкодер — комбинационная схема, которая предназначена для выполнения обратной операции декодера. Кодер имеет n входных линий и m выходных строк. Кодер генерирует m-битный двоичный код, соответствующий номеру цифрового входа. Кодер принимает n входных цифровых слов и преобразует их в m битов в другое цифровое слово.

Блок-схема

Примеры кодеров следующие.

- Приоритетные кодеры

- Десятичный кодировщик в BCD

- Восьмеричное в двоичный кодировщик

- Шестнадцатеричный к двоичному кодеру

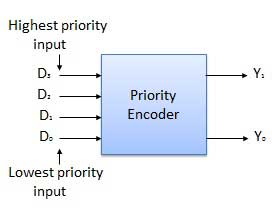

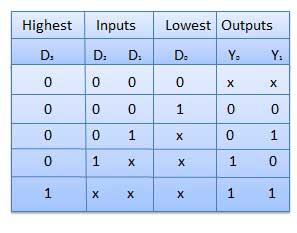

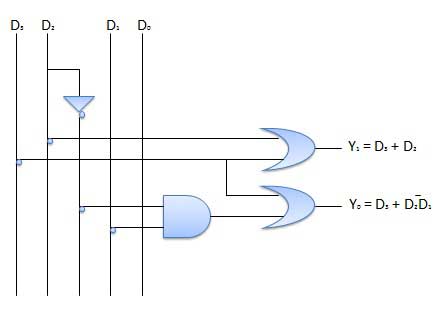

Приоритетный кодировщик

Это особый тип кодировщика. Приоритет отдается линиям ввода. Если две или более строки ввода равны 1, то будет рассматриваться строка ввода с наивысшим приоритетом. Есть четыре входа D 0 , D 1 , D 2 , D 3 и два выхода Y 0 , Y 1 . Из четырех входов D 3 имеет самый высокий приоритет, а D 0 имеет самый низкий приоритет. Это означает, что если D 3 = 1, то Y 1, Y 1 = 11 независимо от других входов. Аналогично, если D 3 = 0 и D 2 = 1, тогда Y 1, Y 0 = 10 независимо от других входов.

Блок-схема

Таблица правды

Логическая схема

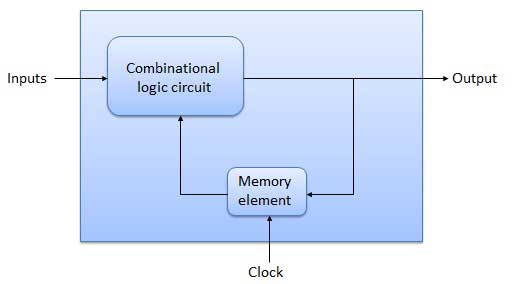

Последовательные цепи

Комбинационная схема не использует никакой памяти. Следовательно, предыдущее состояние входа не влияет на текущее состояние схемы. Но последовательная схема имеет память, поэтому выходной сигнал может варьироваться в зависимости от входа. Этот тип схем использует предыдущий вход, выход, часы и элемент памяти.

Блок-схема

Резкий поворот

Триггер — это последовательная схема, которая обычно производит выборку своих входов и изменяет свои выходы только в определенные моменты времени, а не непрерывно. Считается, что триггер чувствителен к краям или срабатывает по краям, а не по уровню, как защелки.

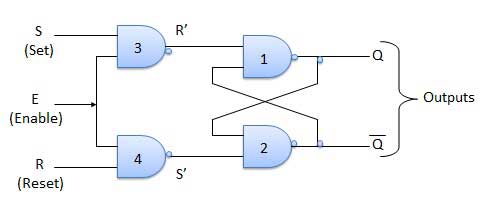

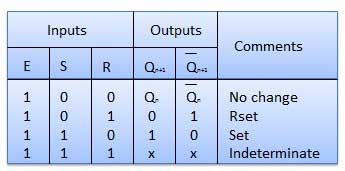

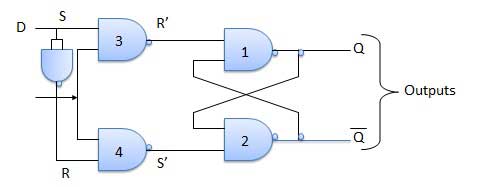

SR флип-флоп

В основном это SR-защелка с использованием NAND-вентилей с дополнительным входом включения . Он также называется уровнем срабатывания SR-FF. Для этого цепь на выходе будет иметь место тогда и только тогда, когда активирован вход разрешения (E). Короче говоря, эта схема будет работать как SR-защелка, если E = 1, но нет изменений в выходе, если E = 0.

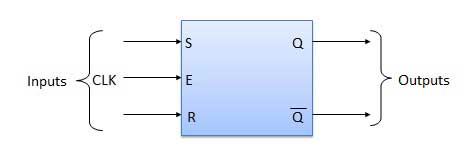

Блок-схема

Принципиальная электрическая схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | S = R = 0: без изменений |

Если S = R = 0, то выходные данные вентилей NAND 3 и 4 принудительно становятся равными 1. Следовательно, R ‘и S’ оба будут равны 1. Поскольку S ‘и R’ являются входом базовой SR-защелки с использованием вентилей NAND, состояние выходов не изменится. |

| 2 | S = 0, R = 1, E = 1 |

Поскольку S = 0, выход NAND-3, т. Е. R ‘= 1, а E = 1, выход NAND-4, т. Е. S’ = 0. Следовательно, Q n + 1 = 0 и Q n + 1 бар = 1. Это условие сброса. |

| 3 | S = 1, R = 0, E = 1 |

Выход NAND-3, т. Е. R ‘= 0, и выход NAND-4, т. Е. S’ = 1. Следовательно, выход SR NAND защелки имеет значение Q n + 1 = 1 и Q n + 1 бар = 0. Это условие сброса. |

| 4 | S = 1, R = 1, E = 1 |

Поскольку S = 1, R = 1 и E = 1, выходные данные вентилей NAND 3 и 4 равны 0, т. Е. S ‘= R’ = 0. Следовательно, состояние гонки будет происходить в базовой защелке NAND. |

Если S = R = 0, то выходные данные вентилей NAND 3 и 4 принудительно становятся равными 1.

Следовательно, R ‘и S’ оба будут равны 1. Поскольку S ‘и R’ являются входом базовой SR-защелки с использованием вентилей NAND, состояние выходов не изменится.

Поскольку S = 0, выход NAND-3, т. Е. R ‘= 1, а E = 1, выход NAND-4, т. Е. S’ = 0.

Следовательно, Q n + 1 = 0 и Q n + 1 бар = 1. Это условие сброса.

Выход NAND-3, т. Е. R ‘= 0, и выход NAND-4, т. Е. S’ = 1.

Следовательно, выход SR NAND защелки имеет значение Q n + 1 = 1 и Q n + 1 бар = 0. Это условие сброса.

Поскольку S = 1, R = 1 и E = 1, выходные данные вентилей NAND 3 и 4 равны 0, т. Е. S ‘= R’ = 0.

Следовательно, состояние гонки будет происходить в базовой защелке NAND.

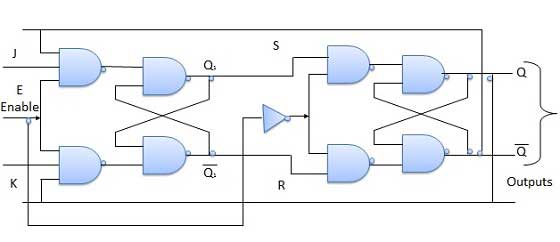

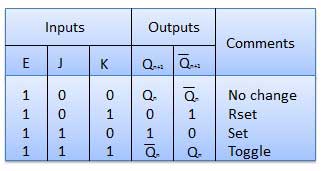

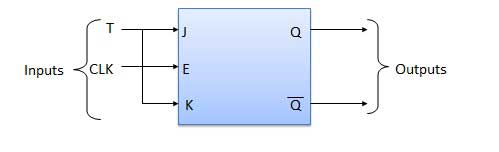

Мастер Раб JK Флип-флоп

Ведомое ведомое устройство JK FF представляет собой каскад из двух SR FF с обратной связью с выхода секунды на вход первого. Мастер положительный уровень срабатывает. Но из-за присутствия инвертора в линии синхронизации ведомый будет реагировать на отрицательный уровень. Следовательно, когда часы = 1 (положительный уровень), ведущий активен, а ведомый неактивен. Принимая во внимание, что когда часы = 0 (низкий уровень), ведомое устройство активно, а ведущее устройство неактивно.

Принципиальная электрическая схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | J = K = 0 (без изменений) |

Когда часы = 0, ведомый становится активным, а ведущий неактивным. Но поскольку входы S и R не изменились, ведомые выходы также останутся неизменными. Поэтому выходы не изменятся, если J = K = 0. |

| 2 | J = 0 и K = 1 (Сброс) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 0 и Q 1 bar = 1. Это означает, что S = 0 и R = 1. Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 0 и Q bar = 1. Снова часы = 1 — Ведущий активен, подчиненный неактивен. Следовательно, даже если измененные выходы Q = 0 и Q bar = 1 возвращены ведущему, его выход будет Q1 = 0 и Q1 bar = 1. Это означает, что S = 0 и R = 1. Следовательно, когда часы = 0 и ведомое устройство становится активным, выходы ведомого устройства останутся Q = 0 и Q bar = 1. Таким образом, мы получим стабильный выход от ведущего ведомого устройства. |

| 3 | J = 1 и K = 0 (Set) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 1 и Q 1 бар = 0. Это означает, что S = 1 и R = 0. Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 1 и Q bar = 0. Снова clock = 1 — тогда можно показать, что выходы ведомого устройства стабилизируются до Q = 1 и Q bar = 0. |

| 4 | J = K = 1 (Переключить) |

Часы = 1 — Ведущий активен, подчиненный неактивен. Выходы мастера будут переключаться. Так что S и R также будут инвертированы. Часы = 0 — Ведомый активен, ведущий неактивен. Выходы раба будут переключаться. Эти измененные выходные данные возвращаются на главные входы. Но так как часы = 0, мастер по-прежнему неактивен. Таким образом, он не реагирует на эти измененные результаты. Это позволяет избежать многократного переключения, которое приводит к гонке вокруг состояния. Мастер-слейв-флип позволит избежать гонки вокруг условия. |

Когда часы = 0, ведомый становится активным, а ведущий неактивным. Но поскольку входы S и R не изменились, ведомые выходы также останутся неизменными. Поэтому выходы не изменятся, если J = K = 0.

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 0 и Q 1 bar = 1. Это означает, что S = 0 и R = 1.

Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 0 и Q bar = 1.

Снова часы = 1 — Ведущий активен, подчиненный неактивен. Следовательно, даже если измененные выходы Q = 0 и Q bar = 1 возвращены ведущему, его выход будет Q1 = 0 и Q1 bar = 1. Это означает, что S = 0 и R = 1.

Следовательно, когда часы = 0 и ведомое устройство становится активным, выходы ведомого устройства останутся Q = 0 и Q bar = 1. Таким образом, мы получим стабильный выход от ведущего ведомого устройства.

Часы = 1 — Ведущий активен, подчиненный неактивен. Поэтому выходы мастера становятся Q 1 = 1 и Q 1 бар = 0. Это означает, что S = 1 и R = 0.

Часы = 0 — Ведомый активен, ведущий неактивен. Поэтому выходы ведомого становятся Q = 1 и Q bar = 0.

Снова clock = 1 — тогда можно показать, что выходы ведомого устройства стабилизируются до Q = 1 и Q bar = 0.

Часы = 1 — Ведущий активен, подчиненный неактивен. Выходы мастера будут переключаться. Так что S и R также будут инвертированы.

Часы = 0 — Ведомый активен, ведущий неактивен. Выходы раба будут переключаться.

Эти измененные выходные данные возвращаются на главные входы. Но так как часы = 0, мастер по-прежнему неактивен. Таким образом, он не реагирует на эти измененные результаты. Это позволяет избежать многократного переключения, которое приводит к гонке вокруг состояния. Мастер-слейв-флип позволит избежать гонки вокруг условия.

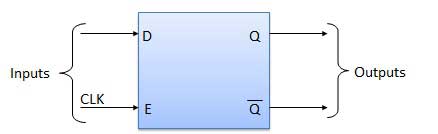

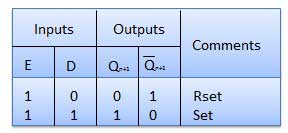

Delay Flip Flop / D Flip Flop

Delay Flip Flop или D Flip Flop — это простая стробированная SR-защелка с инвертором NAND, подключенным между входами S и R. Он имеет только один вход. Входные данные появляются на выходе через некоторое время. Из-за этой задержки данных между i / p и o / p это называется задержкой триггера. S и R будут дополнять друг друга благодаря инвертору NAND. Следовательно, S = R = 0 или S = R = 1, эти входные условия никогда не появятся. Эту проблему можно избежать с помощью условий SR = 00 и SR = 1.

Блок-схема

Принципиальная электрическая схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | E = 0 |

Защелка отключена. Следовательно, никаких изменений в выходе. |

| 2 | E = 1 и D = 0 |

Если E = 1 и D = 0, то S = 0 и R = 1. Следовательно, независимо от текущего состояния, следующим состоянием является Q n + 1 = 0 и Q n + 1 bar = 1. Это условие сброса. |

| 3 | E = 1 и D = 1 |

Если E = 1 и D = 1, то S = 1 и R = 0. Это установит фиксатор и Q n + 1 = 1 и Q n + 1 бар = 0 независимо от текущего состояния. |

Защелка отключена. Следовательно, никаких изменений в выходе.

Если E = 1 и D = 0, то S = 0 и R = 1. Следовательно, независимо от текущего состояния, следующим состоянием является Q n + 1 = 0 и Q n + 1 bar = 1. Это условие сброса.

Если E = 1 и D = 1, то S = 1 и R = 0. Это установит фиксатор и Q n + 1 = 1 и Q n + 1 бар = 0 независимо от текущего состояния.

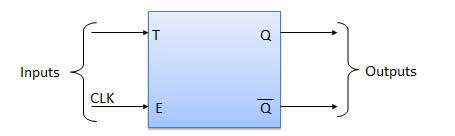

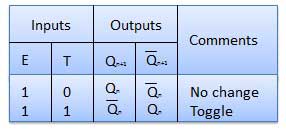

Toggle Flip Flop / T Flip Flop

Триггерный триггер — это в основном триггер JK с постоянно соединенными клеммами J и K. Он имеет только вход, обозначенный буквой T, как показано на диаграмме символов. Символ для триггера с положительным фронтом показан на блок-схеме.

Символьная диаграмма

Блок-схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | T = 0, J = K = 0 | Выходной Q и Q бар не изменится |

| 2 | Т = 1, J = К = 1 | Выход будет переключаться в соответствии с каждым передним фронтом тактового сигнала. |

Цифровые регистры

Триггер представляет собой 1-битную ячейку памяти, которая может использоваться для хранения цифровых данных. Чтобы увеличить объем памяти с точки зрения количества бит, мы должны использовать группу триггеров. Такая группа триггеров называется Регистром . N-битный регистр будет состоять из n номеров триггера, и он способен хранить n-битное слово.

Двоичные данные в регистре можно перемещать в регистре с одного триггера на другой. Регистры, которые позволяют такие передачи данных, называются сдвиговыми регистрами . Существует четыре режима работы сдвигового регистра.

- Последовательный вход Последовательный выход

- Последовательный вход Параллельный выход

- Параллельный вход Последовательный выход

- Параллельный вход Параллельный выход

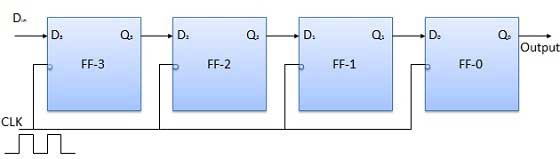

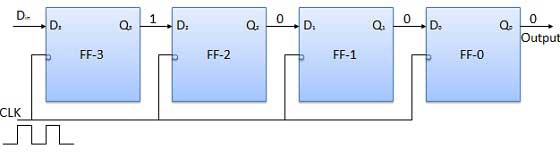

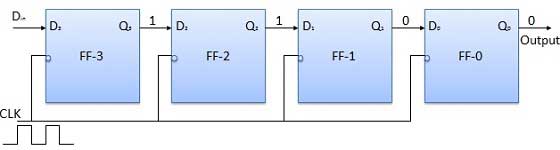

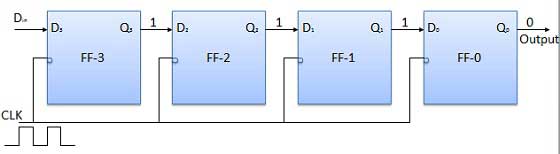

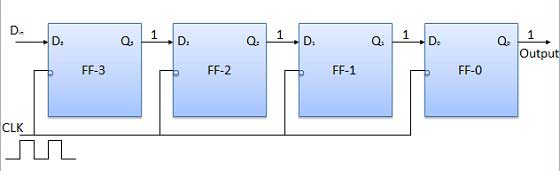

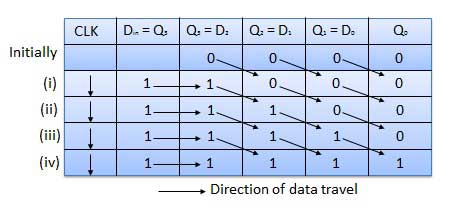

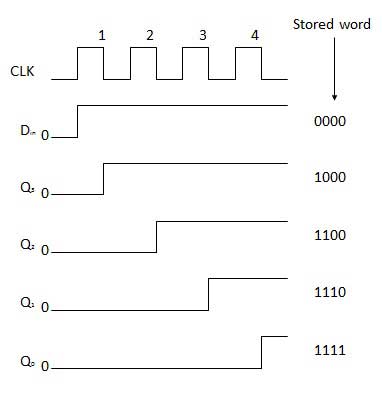

Последовательный вход Последовательный выход

Пусть все триггеры изначально находятся в состоянии сброса, т.е. Q 3 = Q 2 = Q 1 = Q 0 = 0. Если в регистр внесена запись четырехбитового двоичного числа 1 1 1 1, это число должно быть применяется к биту D с битом LSB, примененным первым. Вход D FF-3, т. Е. D 3 , подключен к последовательному входу данных D in . Выход FF-3, т.е. Q 3 , подключен ко входу следующего триггера, т.е. D 2 и так далее.

Блок-схема

операция

Перед применением тактового сигнала, пусть Q 3 Q 2 Q 1 Q 0 = 0000 и применяет бит LSB числа, которое нужно ввести в D in . Так что D в = D 3 = 1. Применить часы. На первом заднем фронте тактовой частоты устанавливается FF-3, и сохраненное слово в регистре имеет вид Q 3 Q 2 Q 1 Q 0 = 1000.

Применить следующий бит к D в . Таким образом, D in = 1. Как только наступит следующий отрицательный фронт тактовых импульсов, FF-2 установится, и сохраненное слово изменится на Q 3 Q 2 Q 1 Q 0 = 1100.

Примените следующий сохраняемый бит, т.е. от 1 до D in . Применить тактовый импульс. Как только третий отрицательный край тактового импульса достигнет значения, будет установлен FF-1 и выходной сигнал будет изменен на Q 3 Q 2 Q 1 Q 0 = 1110.

Аналогично, с D in = 1 и с приходом четвертого отрицательного тактового фронта сохраненное слово в регистре равно Q 3 Q 2 Q 1 Q 0 = 1111.

Таблица правды

Волновые

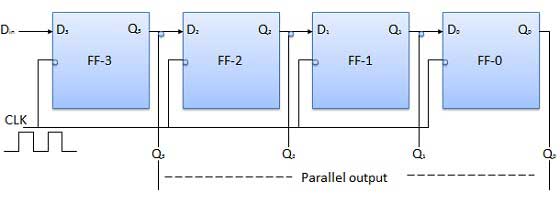

Последовательный вход Параллельный выход

-

При таких типах операций данные вводятся последовательно и выводятся параллельно.

-

Данные загружаются по крупицам. Выходы отключены, пока данные загружаются.

-

Как только загрузка данных завершится, все триггеры содержат свои необходимые данные, выходы будут включены, чтобы все загруженные данные стали доступны по всем выходным линиям одновременно.

-

Для загрузки четырехбитного слова требуется 4 такта. Следовательно, скорость работы в режиме SIPO такая же, как в режиме SISO.

При таких типах операций данные вводятся последовательно и выводятся параллельно.

Данные загружаются по крупицам. Выходы отключены, пока данные загружаются.

Как только загрузка данных завершится, все триггеры содержат свои необходимые данные, выходы будут включены, чтобы все загруженные данные стали доступны по всем выходным линиям одновременно.

Для загрузки четырехбитного слова требуется 4 такта. Следовательно, скорость работы в режиме SIPO такая же, как в режиме SISO.

Блок-схема

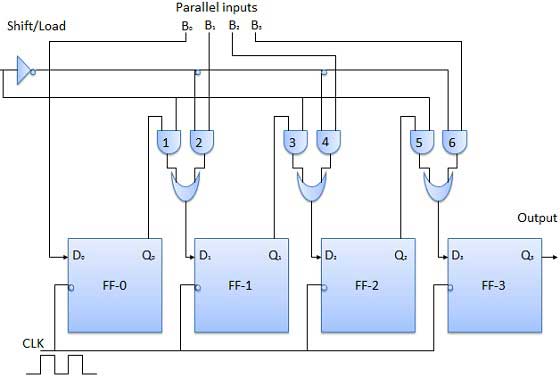

Параллельный вход Последовательный выход (PISO)

-

Биты данных вводятся параллельно.

-

Схема, показанная ниже, представляет собой четырехбитовый параллельный входной регистр последовательного выхода.

-

Выход предыдущего триггера соединен со входом следующего через комбинационную схему.

-

Двоичное входное слово B 0 , B 1 , B 2 , B 3 применяется через одну и ту же комбинационную схему.

-

Есть два режима, в которых может работать эта схема, а именно — режим смещения или режим нагрузки.

Биты данных вводятся параллельно.

Схема, показанная ниже, представляет собой четырехбитовый параллельный входной регистр последовательного выхода.

Выход предыдущего триггера соединен со входом следующего через комбинационную схему.

Двоичное входное слово B 0 , B 1 , B 2 , B 3 применяется через одну и ту же комбинационную схему.

Есть два режима, в которых может работать эта схема, а именно — режим смещения или режим нагрузки.

Режим загрузки

Когда линия сдвига / полосы загрузки является низкой (0), логические элементы И, 2, 4 и 6 становятся активными, они передают биты B 1 , B 2 , B 3 на соответствующие триггеры. На низком фронте тактовой частоты двоичные входы B 0 , B 1 , B 2 , B 3 будут загружены в соответствующие триггеры. Таким образом происходит параллельная загрузка.

Режим сдвига

Когда линия сдвига / полосы нагрузки низкая (1), логические элементы И, 2, 4 и 6 становятся неактивными. Следовательно, параллельная загрузка данных становится невозможной. Но ворота 1,3 и 5 И становятся активными. Поэтому сдвиг данных слева направо по крупицам при применении тактовых импульсов. Таким образом, происходит параллельная операция последовательного вывода.

Блок-схема

Параллельный вход Параллельный выход (PIPO)

В этом режиме 4-битный двоичный вход B 0 , B 1 , B 2 , B 3 применяется к входам данных D 0 , D 1 , D 2 , D 3 соответственно четырех триггеров. Как только отрицательный фронт такта применен, входные двоичные биты будут загружены в триггеры одновременно. Загруженные биты появятся одновременно на выходной стороне. Только тактовый импульс необходим для загрузки всех битов.

Блок-схема

Двунаправленный регистр сдвига

-

Если двоичное число сдвигается влево на одну позицию, то это эквивалентно умножению исходного числа на 2. Аналогично, если двоичное число сдвигается вправо на одну позицию, то это эквивалентно делению исходного числа на 2.

-

Следовательно, если мы хотим использовать сдвиговый регистр для умножения и деления заданного двоичного числа, то мы должны иметь возможность перемещать данные влево или вправо.

-

Такой регистр называется двунаправленным регистром. Четырехбитный двунаправленный регистр сдвига показан на рис.

-

Имеется два последовательных входа, а именно последовательный ввод данных правого сдвига DR и последовательный ввод данных левого сдвига DL вместе с входом выбора режима (M).

Если двоичное число сдвигается влево на одну позицию, то это эквивалентно умножению исходного числа на 2. Аналогично, если двоичное число сдвигается вправо на одну позицию, то это эквивалентно делению исходного числа на 2.

Следовательно, если мы хотим использовать сдвиговый регистр для умножения и деления заданного двоичного числа, то мы должны иметь возможность перемещать данные влево или вправо.

Такой регистр называется двунаправленным регистром. Четырехбитный двунаправленный регистр сдвига показан на рис.

Имеется два последовательных входа, а именно последовательный ввод данных правого сдвига DR и последовательный ввод данных левого сдвига DL вместе с входом выбора режима (M).

Блок-схема

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | С М = 1 — сдвиг вправо |

Если M = 1, то логические элементы AND 1, 3, 5 и 7 включены, тогда как остальные логические элементы AND 2, 4, 6 и 8 будут заблокированы. Данные в D R сдвигаются вправо по битам от FF-3 к FF-0 при применении тактовых импульсов. Таким образом, при M = 1 мы получаем последовательную операцию правого сдвига. |

| 2 | С М = 0 — сдвиг влево |

Когда регулятор режима М подключен к 0, тогда логические элементы И, 2, 4, 6 и 8 включены, а 1, 3, 5 и 7 отключены. Данные в D L сдвигаются влево по битам от FF-0 до FF-3 при применении тактовых импульсов. Таким образом, при M = 0 мы получаем последовательную операцию правого сдвига. |

Если M = 1, то логические элементы AND 1, 3, 5 и 7 включены, тогда как остальные логические элементы AND 2, 4, 6 и 8 будут заблокированы.

Данные в D R сдвигаются вправо по битам от FF-3 к FF-0 при применении тактовых импульсов. Таким образом, при M = 1 мы получаем последовательную операцию правого сдвига.

Когда регулятор режима М подключен к 0, тогда логические элементы И, 2, 4, 6 и 8 включены, а 1, 3, 5 и 7 отключены.

Данные в D L сдвигаются влево по битам от FF-0 до FF-3 при применении тактовых импульсов. Таким образом, при M = 0 мы получаем последовательную операцию правого сдвига.

Универсальный регистр сдвига

Сдвиговый регистр, который может сдвигать данные только в одном направлении, называется однонаправленным сдвиговым регистром. Сдвиговый регистр, который может сдвигать данные в обоих направлениях, называется двунаправленным сдвиговым регистром. Применяя ту же логику, сдвиговый регистр, который может сдвигать данные в обоих направлениях, а также загружать их параллельно, известен как универсальный сдвиговый регистр. Сдвиговый регистр способен выполнять следующую операцию —

- Параллельная загрузка

- Сдвиг влево

- Сдвиг вправо

Вход управления режимом подключен к логике 1 для параллельной загрузки, тогда как он подключен к 0 для последовательного переключения. Когда контакт управления режимом подключен к земле, универсальный регистр сдвига действует как двунаправленный регистр. Для последовательной левой операции ввод применяется к последовательному входу, который идет к логическому элементу AND gate-1, показанному на рисунке. Принимая во внимание, что для операции сдвига вправо, последовательный вход применяется к входу D.

Блок-схема

Цифровые счетчики

Счетчик — это последовательная схема. Цифровая схема, которая используется для подсчета импульсов, является известным счетчиком. Счетчик — самое широкое применение шлепанцев. Это группа триггеров с примененным тактовым сигналом. Счетчики бывают двух типов.

- Асинхронные или пульсирующие счетчики.

- Синхронные счетчики.

Асинхронные или пульсирующие счетчики

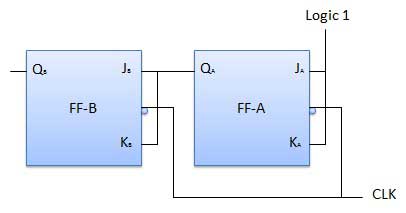

Логическая схема 2-битного счетчика пульсаций показана на рисунке. Триггер (T) используется. Но мы можем использовать триггер JK также с J и K, постоянно подключенными к логике 1. Внешние часы применяются к тактовому входу триггера A, а выход Q A применяется к тактовому входу следующего триггера, т.е. FF-B.

Логическая Диаграмма

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | Сначала позвольте обоим FF быть в состоянии сброса | Q B Q A = 00 изначально |

| 2 | После 1-го отрицательного фронта часов |

Как только первый отрицательный тактовый импульс будет применен, FF-A переключится и Q A будет равно 1. Q A подключен к тактовому входу FF-B. Поскольку Q A изменилось с 0 на 1, FF-B рассматривает его как положительный фронт тактового сигнала. В Q B нет никаких изменений, потому что FF-B является FF, вызванным отрицательным фронтом. Q B Q A = 01 после первого тактового импульса. |

| 3 | После 2-го отрицательного фронта часов |

По прибытии второго отрицательного тактового фронта FF-A снова переключается и Q A = 0. Изменение Q A действует как отрицательный фронт тактовой частоты для FF-B. Так что он также будет переключаться, и Q B будет 1. Q B Q A = 10 после второго тактового импульса. |

| 4 | После 3-го отрицательного тактового фронта |

По достижении 3-го отрицательного тактового фронта FF-A снова переключается, и Q A становится 1 из 0. Поскольку это положительное изменение, FF-B не реагирует на него и остается неактивным. Таким образом, Q B не изменяется и продолжает оставаться равным 1. Q B Q A = 11 после третьего тактового импульса. |

| 5 | После 4-го отрицательного тактового фронта |

По достижении 4-го отрицательного тактового фронта FF-A снова переключается, и Q A становится 1 из 0. Это отрицательное изменение Q A действует как тактовый импульс для FF-B. Следовательно, он переключается, чтобы изменить Q B с 1 на 0. Q B Q A = 00 после четвертого тактового импульса. |

Как только первый отрицательный тактовый импульс будет применен, FF-A переключится и Q A будет равно 1.

Q A подключен к тактовому входу FF-B. Поскольку Q A изменилось с 0 на 1, FF-B рассматривает его как положительный фронт тактового сигнала. В Q B нет никаких изменений, потому что FF-B является FF, вызванным отрицательным фронтом.

Q B Q A = 01 после первого тактового импульса.

По прибытии второго отрицательного тактового фронта FF-A снова переключается и Q A = 0.

Изменение Q A действует как отрицательный фронт тактовой частоты для FF-B. Так что он также будет переключаться, и Q B будет 1.

Q B Q A = 10 после второго тактового импульса.

По достижении 3-го отрицательного тактового фронта FF-A снова переключается, и Q A становится 1 из 0.

Поскольку это положительное изменение, FF-B не реагирует на него и остается неактивным. Таким образом, Q B не изменяется и продолжает оставаться равным 1.

Q B Q A = 11 после третьего тактового импульса.

По достижении 4-го отрицательного тактового фронта FF-A снова переключается, и Q A становится 1 из 0.

Это отрицательное изменение Q A действует как тактовый импульс для FF-B. Следовательно, он переключается, чтобы изменить Q B с 1 на 0.

Q B Q A = 00 после четвертого тактового импульса.

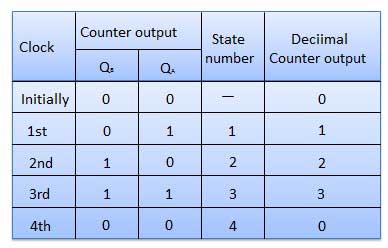

Таблица правды

Синхронные счетчики

Если тактовые импульсы применяются ко всем триггерам в счетчике одновременно, то такой счетчик называется синхронным счетчиком.

2-битный синхронный счетчик

Входы J A и K A FF-A связаны с логикой 1. Таким образом, FF-A будет работать как триггерный триггер. Входы J B и K B подключены к Q A.

Логическая Диаграмма

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | Сначала позвольте обоим FF быть в состоянии сброса | Q B Q A = 00 изначально. |

| 2 | После 1-го отрицательного фронта часов |

Как только будет применен первый отрицательный фронт тактового сигнала, FF-A переключится и Q A изменится с 0 на 1. Но в момент приложения отрицательного тактового фронта Q A , J B = K B = 0. Следовательно, FF-B не изменит свое состояние. Таким образом, Q B останется 0. Q B Q A = 01 после первого тактового импульса. |

| 3 | После 2-го отрицательного фронта часов |

По прибытии второго отрицательного фронта тактового сигнала FF-A снова переключается, и Q A изменяется с 1 на 0. Но в этот момент Q A было 1. Таким образом, J B = K B = 1 и FF-B будет переключаться. Следовательно, Q B изменяется от 0 до 1. Q B Q A = 10 после второго тактового импульса. |

| 4 | После 3-го отрицательного тактового фронта |

При применении третьего падающего тактового фронта FF-A переключается с 0 на 1, но для FF-B состояние не изменяется. Q B Q A = 11 после третьего тактового импульса. |

| 5 | После 4-го отрицательного тактового фронта |

При применении следующего тактового импульса Q A изменится с 1 на 0, а Q B также изменится с 1 на 0. Q B Q A = 00 после четвертого тактового импульса. |

Как только будет применен первый отрицательный фронт тактового сигнала, FF-A переключится и Q A изменится с 0 на 1.

Но в момент приложения отрицательного тактового фронта Q A , J B = K B = 0. Следовательно, FF-B не изменит свое состояние. Таким образом, Q B останется 0.

Q B Q A = 01 после первого тактового импульса.

По прибытии второго отрицательного фронта тактового сигнала FF-A снова переключается, и Q A изменяется с 1 на 0.

Но в этот момент Q A было 1. Таким образом, J B = K B = 1 и FF-B будет переключаться. Следовательно, Q B изменяется от 0 до 1.

Q B Q A = 10 после второго тактового импульса.

При применении третьего падающего тактового фронта FF-A переключается с 0 на 1, но для FF-B состояние не изменяется.

Q B Q A = 11 после третьего тактового импульса.

При применении следующего тактового импульса Q A изменится с 1 на 0, а Q B также изменится с 1 на 0.

Q B Q A = 00 после четвертого тактового импульса.

Классификация счетчиков

В зависимости от того, как происходит процесс подсчета, синхронные или асинхронные счетчики классифицируются следующим образом:

- Счетчики вверх

- Вниз счетчики

- Счетчики вверх / вниз

Счетчик UP / DOWN

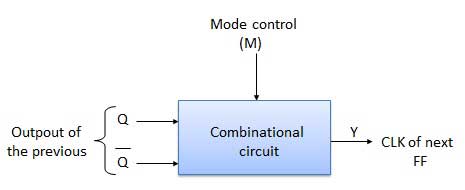

Верхний и нижний счетчики объединяются, чтобы получить счетчик ВВЕРХ / ВНИЗ. Вход управления режимом (M) также предназначен для выбора режима вверх или вниз. Комбинационная схема должна быть спроектирована и использована между каждой парой триггера для достижения операции вверх / вниз.

- Тип счетчиков вверх / вниз

- Счетчики пульсаций ВВЕРХ / ВНИЗ

- Синхронный счетчик UP / DOWN

Счетчики пульсаций ВВЕРХ / ВНИЗ

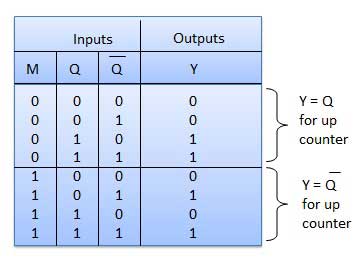

В счетчике пульсаций UP / DOWN все FF работают в режиме переключения. Поэтому следует использовать либо T-триггеры, либо JK-триггеры. LSB триггер получает часы напрямую. Но часы для каждого другого FF получаются из (Q = Q bar) выходного сигнала предыдущего FF.

-

Режим счета UP (M = 0) — Выход Q предыдущего FF подключен к часам следующего каскада, если необходимо увеличить счет. Для этого режима вход выбора режима М имеет логическую 0 (М = 0).

-

Режим подсчета ВНИЗ (M = 1) — Если M = 1, то выход Q-бара предыдущего FF подключается к следующему FF. Это будет работать счетчик в режиме счета.

Режим счета UP (M = 0) — Выход Q предыдущего FF подключен к часам следующего каскада, если необходимо увеличить счет. Для этого режима вход выбора режима М имеет логическую 0 (М = 0).

Режим подсчета ВНИЗ (M = 1) — Если M = 1, то выход Q-бара предыдущего FF подключается к следующему FF. Это будет работать счетчик в режиме счета.

пример

3-битный двоичный счетчик пульсаций вверх / вниз.

-

3-битный — следовательно, требуется три FF.

-

ВВЕРХ / ВНИЗ — так что вход управления режимом имеет важное значение.

-

Для счетчика пульсаций выход Q предыдущего FF подключен к входу тактового сигнала следующего.

-

Для счетчика пульсаций выход Q предыдущего FF подключен к входу тактового сигнала следующего.

-

Для счетчика пульсаций выход Q bar предыдущего FF соединяется с тактовым входом следующего.

-

Пусть выбор выхода Q и Q bar предыдущего FF управляется входом управления режимом M таким образом, что, если M = 0, счет UP. Так что подключите Q к CLK. Если М = 1, счет ВНИЗ. Так что подключите Q бар к CLK.

3-битный — следовательно, требуется три FF.

ВВЕРХ / ВНИЗ — так что вход управления режимом имеет важное значение.

Для счетчика пульсаций выход Q предыдущего FF подключен к входу тактового сигнала следующего.

Для счетчика пульсаций выход Q предыдущего FF подключен к входу тактового сигнала следующего.

Для счетчика пульсаций выход Q bar предыдущего FF соединяется с тактовым входом следующего.

Пусть выбор выхода Q и Q bar предыдущего FF управляется входом управления режимом M таким образом, что, если M = 0, счет UP. Так что подключите Q к CLK. Если М = 1, счет ВНИЗ. Так что подключите Q бар к CLK.

Блок-схема

Таблица правды

операция

| SN | Состояние | операция |

|---|---|---|

| 1 | Случай 1 — с М = 0 (режим повышенного счета) |

Если M = 0 и M bar = 1, то логические элементы И 1 и 3 на рис. будет включен, тогда как логические элементы И 2 и 4 будут отключены. Следовательно, Q A подключается к входу синхронизации FF-B, а Q B подключается к входу синхронизации FF-C. Эти соединения такие же, как и для обычного счетчика. Таким образом, при М = 0 схема работает как счетчик с повышением частоты. |

| 2 | Случай 2: с М = 1 (режим обратного отсчета) |

Если M = 1, то И вентили 2 и 4 на рис. включены, тогда как логические элементы И 1 и 3 отключены. Следовательно, панель Q A подключается к тактовому входу FF-B, а панель Q B подключается к тактовому входу FF-C. Эти соединения будут производить обратный счетчик. Таким образом, при М = 1 схема работает как обратный счетчик. |

Если M = 0 и M bar = 1, то логические элементы И 1 и 3 на рис. будет включен, тогда как логические элементы И 2 и 4 будут отключены.

Следовательно, Q A подключается к входу синхронизации FF-B, а Q B подключается к входу синхронизации FF-C.

Эти соединения такие же, как и для обычного счетчика. Таким образом, при М = 0 схема работает как счетчик с повышением частоты.

Если M = 1, то И вентили 2 и 4 на рис. включены, тогда как логические элементы И 1 и 3 отключены.

Следовательно, панель Q A подключается к тактовому входу FF-B, а панель Q B подключается к тактовому входу FF-C.

Эти соединения будут производить обратный счетчик. Таким образом, при М = 1 схема работает как обратный счетчик.

Счетчик модулей (Счетчик MOD-N)

2-битный счетчик пульсаций называется счетчиком MOD-4, а 3-битный счетчик пульсаций называется счетчиком MOD-8. Таким образом, в общем случае n-битный счетчик пульсаций называется счетчиком по модулю N. Где, MOD номер = 2 н .

Тип модуля

- 2-битный вверх или вниз (MOD-4)

- 3 бита вверх или вниз (MOD-8)

- 4 бита вверх или вниз (MOD-16)

Применение счетчиков

- Частотомер

- Цифровые часы

- Измерение времени

- А в D конвертер

- Схемы делителя частоты

- Цифровой генератор треугольных волн.

Устройства памяти

Память как человеческий мозг. Он используется для хранения данных и инструкций. Компьютерная память — это пространство хранения на компьютере, где должны обрабатываться данные и храниться инструкции, необходимые для обработки.

Память делится на большое количество мелких частей. Каждая часть называется ячейкой. Каждое местоположение или ячейка имеет уникальный адрес, который варьируется от нуля до объема памяти минус один.

Например, если на компьютере имеется 64 тыс. Слов, этот блок памяти имеет 64 * 1024 = 65536 ячеек памяти. Адрес этих мест варьируется от 0 до 65535.

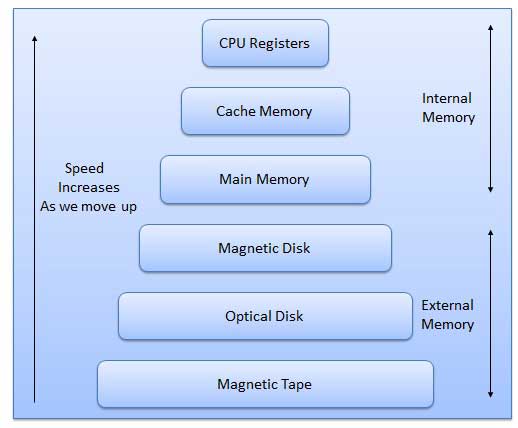

Память в основном двух типов

-

Внутренняя память — кэш-память и основная / основная память

-

Внешняя память — магнитный диск / оптический диск и т. Д.

Внутренняя память — кэш-память и основная / основная память

Внешняя память — магнитный диск / оптический диск и т. Д.

Характеристики иерархии памяти следующие, когда мы идем сверху вниз.

- Емкость с точки зрения хранения увеличивается.

- Стоимость за бит хранения уменьшается.

- Частота доступа памяти к процессору уменьшается.

- Время доступа ЦП увеличивается.

баран

ОЗУ представляет собой внутреннюю память ЦП для хранения данных, программы и результата программы. Это память чтения / записи. Это называется оперативной памятью (RAM).

Поскольку время доступа в ОЗУ не зависит от адреса к слову, то есть каждое место хранения в памяти так же легко доступно, как и другое место, и занимает столько же времени. Мы можем получить доступ к памяти произвольно и очень быстро, но это может быть довольно дорого.

Оперативная память нестабильна, т.е. данные, хранящиеся в ней, теряются при выключении компьютера или при сбое питания. Следовательно, резервная система бесперебойного питания (ИБП) часто используется с компьютерами. Объем оперативной памяти невелик, как с точки зрения ее физического размера, так и объема данных, которые она может хранить.

Оперативная память бывает двух типов

- Статическая RAM (SRAM)

- Динамическое ОЗУ (DRAM)

Статическая RAM (SRAM)

Слово статическое указывает на то, что память сохраняет свое содержимое, пока питание остается включенным. Однако данные теряются при отключении питания из-за нестабильности. Микросхемы SRAM используют матрицу из 6 транзисторов и без конденсаторов. Транзисторам не требуется питание для предотвращения утечек, поэтому нет необходимости регулярно обновлять SRAM.

Из-за дополнительного места в матрице SRAM использует больше чипов, чем DRAM для того же объема памяти, что увеличивает производственные затраты.

Статическая ОЗУ используется, поскольку кэш-память должна быть очень быстрой и небольшой.

Динамическое ОЗУ (DRAM)

DRAM, в отличие от SRAM, должен постоянно обновляться , чтобы поддерживать данные. Это делается путем помещения памяти в схему обновления, которая перезаписывает данные несколько сотен раз в секунду. DRAM используется для большей части системной памяти, потому что это дешево и мало. Все DRAM состоят из ячеек памяти. Эти ячейки состоят из одного конденсатора и одного транзистора.

ПЗУ

ROM расшифровывается как постоянная память. Память, из которой мы можем только читать, но не можем писать на ней. Этот тип памяти энергонезависимый. Информация постоянно хранится в такой памяти в процессе производства.

В ПЗУ хранятся такие инструкции, которые требуются для запуска компьютера при первом включении электричества, эта операция называется начальной загрузкой. Чип ПЗУ используется не только в компьютере, но и в других электронных устройствах, таких как стиральная машина и микроволновая печь.

Ниже приведены различные типы ПЗУ —

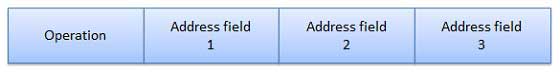

MROM (ПЗУ в маске)