Комбинационная схема — это схема, в которой мы объединяем различные элементы схемы, например, кодер, декодер, мультиплексор и демультиплексор. Некоторые характеристики комбинационных схем следующие —

-

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

-

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

-

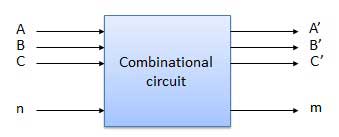

Комбинационная схема может иметь n входов и m выходов.

Выход комбинационной цепи в любой момент времени зависит только от уровней, присутствующих на входных клеммах.

Комбинационная схема не использует никакой памяти. Предыдущее состояние входа не влияет на текущее состояние схемы.

Комбинационная схема может иметь n входов и m выходов.

Блок-схема

Мы собираемся разработать несколько важных комбинационных схем следующим образом.

Полумесяц

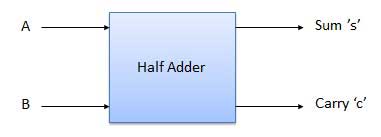

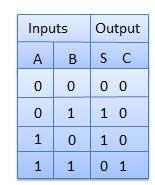

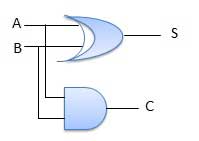

Половина сумматора представляет собой комбинационную логическую схему с двумя входами и двумя выходами. Схема полусумметра предназначена для сложения двух однобитовых двоичных чисел A и B. Это базовый строительный блок для сложения двух однобитовых чисел. Эта схема имеет два выхода переноса и суммы .

Блок-схема

Таблица правды

Принципиальная электрическая схема

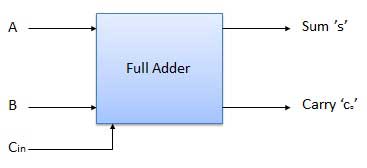

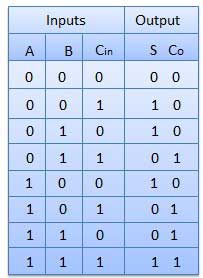

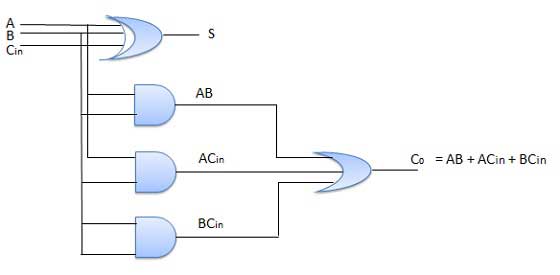

Полный сумматор

Полный сумматор разработан, чтобы преодолеть недостаток схемы Half Adder. Он может добавлять два однобитных числа A и B и переносить c. Полный сумматор представляет собой комбинацию из трех входов и двух выходов.

Блок-схема

Таблица правды

Принципиальная электрическая схема

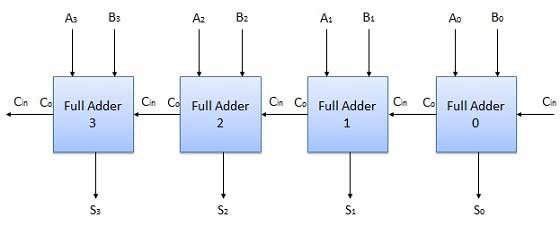

N-битный параллельный сумматор

Полный сумматор способен добавлять только два однозначных двоичных числа вместе с вводом переноса. Но на практике нам нужно добавить двоичные числа, которые намного длиннее одного бита. Чтобы добавить два n-битных двоичных числа, нам нужно использовать n-битный параллельный сумматор. Он использует несколько полных сумматоров в каскаде. Выход переноса предыдущего полного сумматора соединен с вводом переноса следующего полного сумматора.

4-битный параллельный сумматор

На блок-схеме A 0 и B 0 представляют младший бит четырехбитовых слов A и B. Следовательно, Full Adder-0 является самой низкой ступенью. Следовательно, его C in постоянно равен 0. Остальные соединения точно такие же, как у n-битного параллельного сумматора, показанного на рис. Четырехбитный параллельный сумматор — очень распространенная логическая схема.

Блок-схема

N-разрядный параллельный вычитатель

Вычитание можно выполнить, взяв 1 или 2 в дополнение к числу, которое должно быть вычтено. Например, мы можем выполнить вычитание (AB), добавив 1 или 2 в дополнение к B к A. Это означает, что мы можем использовать двоичный сумматор для выполнения двоичного вычитания.

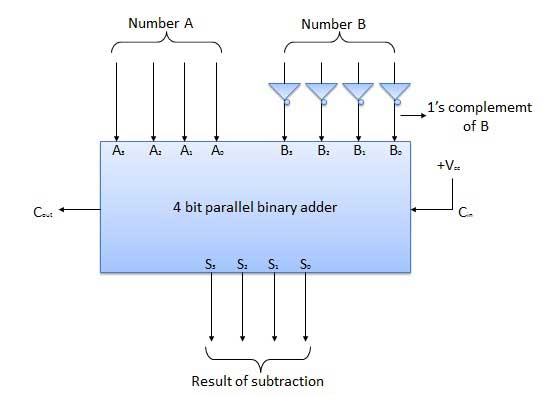

4-битный параллельный вычитатель

Вычитаемое число (B) сначала пропускается через инверторы для получения дополнения к 1. Затем 4-разрядный сумматор добавляет A и 2 к B для вычитания. S 3 S 2 S 1 S 0 представляет результат двоичного вычитания (AB), а выходной сигнал C out представляет полярность результата. Если A> B, то Cout = 0 и результат двоичной формы (AB), тогда C out = 1, и результат находится в форме дополнения 2.

Блок-схема

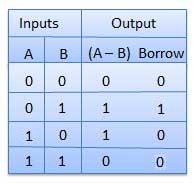

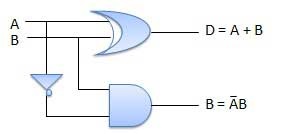

Половина вычитателей

Половина вычитателя представляет собой комбинированную схему с двумя входами и двумя выходами (разность и заем). Он выдает разницу между двумя двоичными битами на входе, а также выводит (заимствовать), чтобы указать, был ли заимствован 1. В вычитании (AB) A называется битом Minuend, а B называется битом Subtrahend.

Таблица правды

Принципиальная электрическая схема

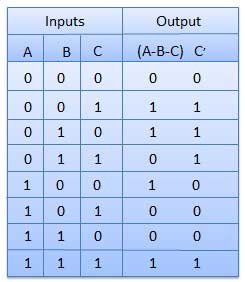

Полные вычитатели

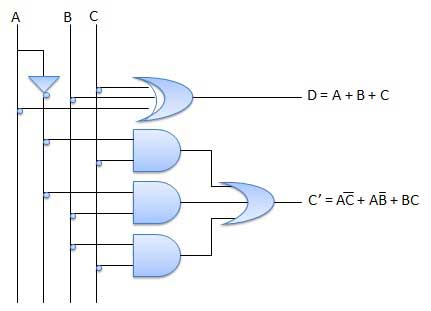

Недостаток половины вычитателя преодолевается полным вычитателем. Полный вычитатель представляет собой комбинационную схему с тремя входами A, B, C и двумя выходами D и C ‘. A — это «minuend», B — «вычитаемое», C — «заем», полученный на предыдущем этапе, D — это результат разницы, а C «- результат заимствования».

Таблица правды

Принципиальная электрическая схема

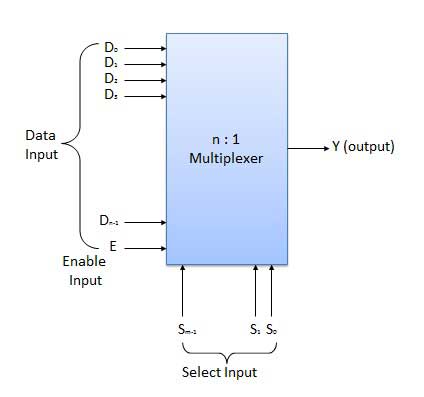

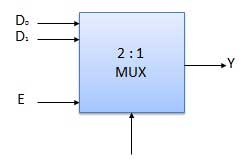

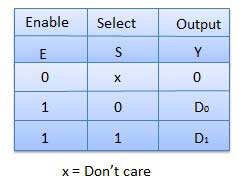

мультиплексоры

Мультиплексор — это особый тип комбинационной схемы. Есть n входов данных, один выход и m выбор входа с 2m = n. Это цифровая схема, которая выбирает один из n входов данных и направляет его на выход. Выбор одного из n входов осуществляется выбранными входами. В зависимости от цифрового кода, применяемого на выбранных входах, один из n источников данных выбирается и передается на один выход Y. E называется стробирующим или разрешающим входом, который полезен для каскадирования. Обычно это активный терминал низкого уровня, что означает, что он будет выполнять требуемую операцию, когда он низкий.

Блок-схема

Мультиплексоры бывают разных вариантов

- Мультиплексор 2: 1

- Мультиплексор 4: 1

- Мультиплексор 16: 1

- Мультиплексор 32: 1

Блок-схема

Таблица правды

демультиплексоры

Демультиплексор выполняет обратную операцию мультиплексора, то есть он получает один вход и распределяет его по нескольким выходам. Он имеет только один вход, n выходов, m выбор входа. Одновременно выбирается только одна выходная строка, и вход передается на выбранную выходную строку. Демультиплексор эквивалентен однополюсному многоходовому переключателю, как показано на рис.

Демультиплексоры выпускаются в нескольких вариантах.

- Демультиплексор 1: 2

- Демультиплексор 1: 4

- Демультиплексор 1:16

- Демультиплексор 1:32

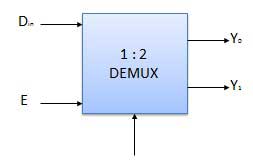

Блок-схема

Таблица правды

дешифратор

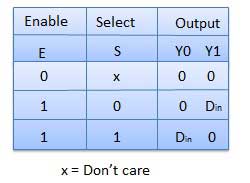

Декодер — комбинационная схема. Он имеет n входов и максимум m = 2n выходов. Декодер идентичен демультиплексору без ввода данных. Он выполняет операции, которые в точности противоположны кодировщику.

Блок-схема

Примеры декодеров следующие.

- Преобразователи кода

- BCD до семи сегментных декодеров

- Nixie ламповые декодеры

- Релейный привод

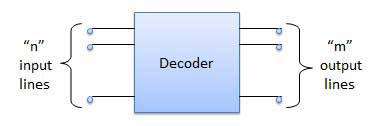

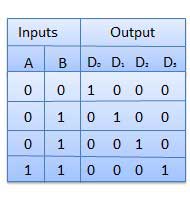

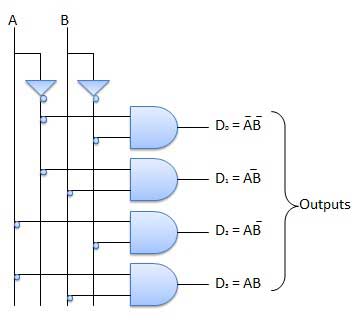

2 до 4-х строчный декодер

Блок-схема 2-4 линейного декодера показана на рис. A и B — два входа, где от D до D — четыре выхода. Таблица правды объясняет операции декодера. Это показывает, что каждый выход равен 1 только для определенной комбинации входов.

Блок-схема

Таблица правды

Логическая схема

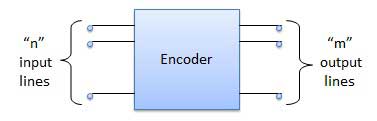

кодировщик

Энкодер — комбинационная схема, которая предназначена для выполнения обратной операции декодера. Кодер имеет n входных линий и m выходных строк. Кодер генерирует m-битный двоичный код, соответствующий номеру цифрового входа. Кодер принимает n входных цифровых слов и преобразует их в m битов в другое цифровое слово.

Блок-схема

Примеры кодеров следующие.

- Приоритетные кодеры

- Десятичный кодировщик в BCD

- Восьмеричное в двоичный кодировщик

- Шестнадцатеричный к двоичному кодеру

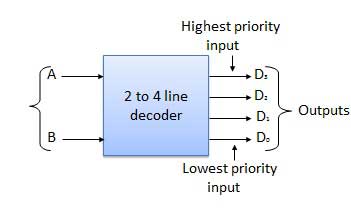

Приоритетный кодировщик

Это особый тип кодировщика. Приоритет отдается линиям ввода. Если две или более строки ввода равны 1, то будет рассматриваться строка ввода с наивысшим приоритетом. Есть четыре входа D 0 , D 1 , D 2 , D 3 и два выхода Y 0 , Y 1 . Из четырех входов D 3 имеет самый высокий приоритет, а D 0 имеет самый низкий приоритет. Это означает, что если D 3 = 1, то Y 1, Y 1 = 11 независимо от других входов. Аналогично, если D 3 = 0 и D 2 = 1, тогда Y 1, Y 0 = 10 независимо от других входов.