Цифро-аналоговый преобразователь (ЦАП) преобразует цифровой входной сигнал в аналоговый выходной сигнал. Цифровой сигнал представлен двоичным кодом, который представляет собой комбинацию битов 0 и 1. В этой главе подробно рассматриваются цифроаналоговые преобразователи.

Блок-схема ЦАП показана на следующем рисунке —

Цифро-аналоговый преобразователь (ЦАП) состоит из нескольких двоичных входов и одного выхода. В общем, число двоичных входов ЦАП будет степенью двойки.

Типы ЦАПов

Есть два типа ЦАПов

- Взвешенный резистор ЦАП

- Лестница ЦАП Р-2Р

В этом разделе подробно рассматриваются эти два типа ЦАП —

Взвешенный резистор ЦАП

Взвешенный резистор ЦАП производит аналоговый выход, который практически равен цифровому (двоичному) входу, используя двоичные взвешенные резисторы в схеме инвертирующего сумматора. Вкратце, бинарный взвешенный резистор DAC называется взвешенным резистором DAC.

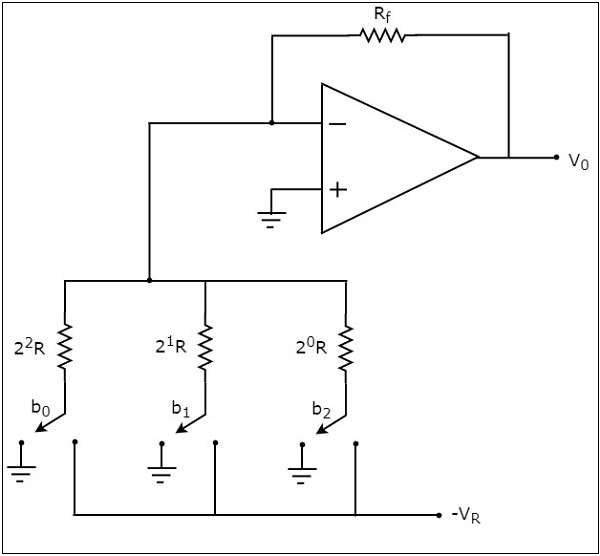

Принципиальная схема 3-разрядного двоичного взвешенного резистора ЦАП показана на следующем рисунке —

Напомним, что биты двоичного числа могут иметь только одно из двух значений. т. е. 0 или 1. Пусть 3-битный двоичный вход равен b2b1b0. Здесь биты b2 и b0 обозначают старший значащий бит (MSB) и младший значащий бит (LSB) соответственно.

Цифровые переключатели, показанные на рисунке выше, будут подключены к заземлению, когда соответствующие входные биты равны «0». Аналогичным образом, цифровые переключатели, показанные на рисунке выше будут соединены с отрицательным опорным напряжением, −VR, когда соответствующие входные биты равны «1».

В вышеупомянутой схеме неинвертирующий входной терминал операционного усилителя соединен с землей. Это означает, что на неинвертирующий входной вывод операционного усилителя подается нулевое напряжение.

Согласно концепции виртуального короткого замыкания , напряжение на инвертирующей входной клемме операционного усилителя такое же, как и напряжение на его неинвертирующей входной клемме. Таким образом, напряжение на узле инвертирующего входного терминала будет равно нулю.

Узловое уравнение в узле инвертирующего входного терминала:

гидроразрыва0+VRB220R+ гидроразрыва0+VRB121R+ гидроразрыва0+VRB022R+ гидроразрыва0−V0Rе=0

=> гидроразрываV0Rе= гидроразрываVRB220R+ гидроразрываVRB121R+ гидроразрываVRB022R

=> V_ {0} = \ frac {V_ {R} R_ {f}} {R} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1 }} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \}

Подставляя, R=2Rf ? в вышеприведенном уравнении.

=> V_ {0} = \ frac {V_ {R} R_ {f}} {2R_ {f}} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac { b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \}

=> V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \}

Вышеупомянутое уравнение представляет уравнение выходного напряжения 3-разрядного двоичного взвешенного резистора ЦАП. Так как число битов три в двоичной (цифровой) вход, мы получим семь возможных значений выходного напряжения путем изменения двоичного входа от 000 до 111 для фиксированного опорного напряжения, VR.

Мы можем записать обобщенное уравнение выходного напряжения N-разрядного двоичного взвешенного резистора DAC, как показано ниже, на основе уравнения выходного напряжения 3-разрядного двоичного взвешенного резистора DAC.

=> V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {N-1}} {2 ^ {0}} + \ frac {b_ {N-2 }} {2 ^ {1}} + …. + \ frac {b_ {0}} {2 ^ {N-1}} \ right \}

Недостатки бинарного взвешенного резистора ЦАП заключаются в следующем —

-

Разница между значениями сопротивления, соответствующими LSB и MSB, будет увеличиваться по мере увеличения количества битов, присутствующих на цифровом входе.

-

Трудно разработать более точные резисторы, поскольку число битов на цифровом входе увеличивается.

Разница между значениями сопротивления, соответствующими LSB и MSB, будет увеличиваться по мере увеличения количества битов, присутствующих на цифровом входе.

Трудно разработать более точные резисторы, поскольку число битов на цифровом входе увеличивается.

Лестница ЦАП Р-2Р

ЦАП R-2R Ladder преодолевает недостатки бинарного взвешенного резистора DAC. Как следует из названия, лестничный ЦАП R-2R производит аналоговый выход, который почти равен цифровому (двоичному) входу, используя лестничную сеть R-2R в схеме инвертирующего сумматора.

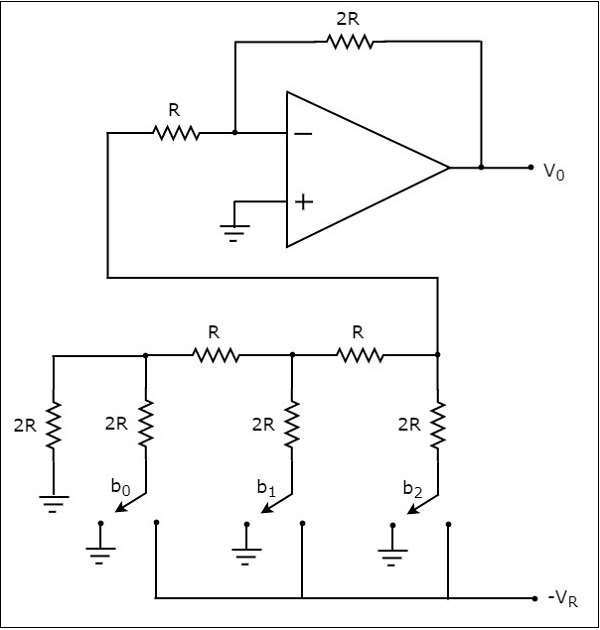

Принципиальная схема 3-битного ЦАП R-2R Ladder показана на следующем рисунке —

Напомним, что биты двоичного числа могут иметь только одно из двух значений. т. е. 0 или 1. Пусть 3-битный двоичный вход равен b2b1b0. Здесь биты b2 и b0 обозначают старший значащий бит (MSB) и младший значащий бит (LSB) соответственно.

Цифровые переключатели, показанные на рисунке выше, будут подключены к заземлению, когда соответствующие входные биты равны «0». Аналогичным образом, цифровые переключатели, показанные на рисунке выше будут соединены с отрицательным опорным напряжением, −VR, когда соответствующие входные биты равны «1».

Трудно получить обобщенное уравнение выходного напряжения лестничного ЦАП R-2R. Но мы можем легко найти значения аналогового выходного напряжения R-2R Ladder DAC для отдельных комбинаций двоичных входов.

Преимущества лестничного ЦАП R-2R заключаются в следующем —

-

R-2R Ladder DAC содержит только два значения резистора: R и 2R. Таким образом, легко выбрать и спроектировать более точные резисторы.

-

Если на цифровом входе присутствует большее количество битов, то мы должны дополнительно включить требуемое количество секций R-2R.

R-2R Ladder DAC содержит только два значения резистора: R и 2R. Таким образом, легко выбрать и спроектировать более точные резисторы.

Если на цифровом входе присутствует большее количество битов, то мы должны дополнительно включить требуемое количество секций R-2R.

Из-за вышеупомянутых преимуществ лестничный ЦАП R-2R предпочтительнее двоичного взвешенного резистора ЦАП.