Микросхема 555 Timer получила свое название от трех резисторов 5K Omega, которые используются в ее сети делителя напряжения. Эта микросхема полезна для генерации точных временных задержек и колебаний. В этой главе подробно рассказывается о таймере 555.

Пин-схема и функциональная схема

В этом разделе сначала давайте обсудим схему выводов 555 таймера IC, а затем ее функциональную схему.

Пин Диаграмма

ИС таймера 555 представляет собой 8-контактный мини-разъем типа Dual-Inline (DIP). Схема контактов микросхемы таймера 555 показана на следующем рисунке.

Значение каждого вывода самоочевидно из вышеприведенной диаграммы. Эта 555 таймер IC может работать с источником постоянного тока от + 5В до + 18В. Это в основном полезно для генерации несинусоидальных волновых форм, таких как квадрат, рампа, импульс и т. Д.

Функциональная схема

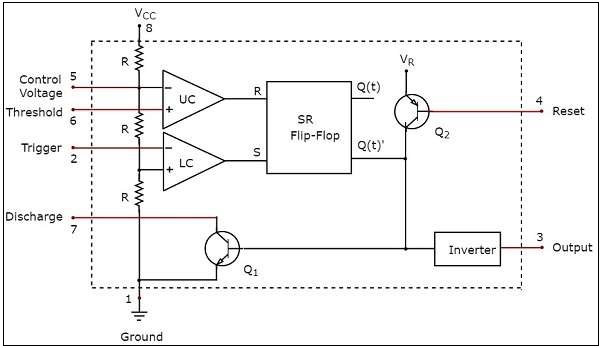

Графическое представление, показывающее внутренние детали таймера 555, называется функциональной схемой.

Функциональная схема 555 таймера IC показана на следующем рисунке —

Обратите внимание, что функциональная схема таймера 555 содержит сеть делителя напряжения, два компаратора, один триггер SR, два транзистора и инвертор. В этом разделе подробно рассматривается назначение каждого блока или компонента —

Сеть делителя напряжения

-

Сеть делителей напряжения состоит из трех резисторов 5K Omega, которые соединены последовательно между напряжением питания Vcc и землей.

-

Эта сеть обеспечивает напряжение fracVcc3 между точкой и землей, если существует только один резистор 5K Omega. Точно так же он обеспечивает напряжение frac2Vcc3 между точкой и землей, если существует только два резистора 5K Omega.

Сеть делителей напряжения состоит из трех резисторов 5K Omega, которые соединены последовательно между напряжением питания Vcc и землей.

Эта сеть обеспечивает напряжение fracVcc3 между точкой и землей, если существует только один резистор 5K Omega. Точно так же он обеспечивает напряжение frac2Vcc3 между точкой и землей, если существует только два резистора 5K Omega.

компаратор

-

Функциональная схема 555 таймера ИС состоит из двух компараторов: верхнего компаратора (UC) и нижнего компаратора (LC).

-

Напомним, что компаратор сравнивает два входных сигнала, которые применяются к нему, и создает выходной сигнал.

-

Если напряжение, присутствующее на неинвертирующей клемме операционного усилителя, больше, чем напряжение на его инвертирующей клемме, то выход компаратора будет равен +Vsat. Это можно рассматривать как высокий логический уровень (‘1’) в цифровом представлении.

-

Если напряжение, присутствующее на неинвертирующей клемме операционного усилителя, меньше или равно напряжению на его инвертирующей клемме, то выход компаратора будет равен −Vsat. Это можно рассматривать как низкий уровень логики (‘0’) в цифровом представлении.

Функциональная схема 555 таймера ИС состоит из двух компараторов: верхнего компаратора (UC) и нижнего компаратора (LC).

Напомним, что компаратор сравнивает два входных сигнала, которые применяются к нему, и создает выходной сигнал.

Если напряжение, присутствующее на неинвертирующей клемме операционного усилителя, больше, чем напряжение на его инвертирующей клемме, то выход компаратора будет равен +Vsat. Это можно рассматривать как высокий логический уровень (‘1’) в цифровом представлении.

Если напряжение, присутствующее на неинвертирующей клемме операционного усилителя, меньше или равно напряжению на его инвертирующей клемме, то выход компаратора будет равен −Vsat. Это можно рассматривать как низкий уровень логики (‘0’) в цифровом представлении.

SR Flip-Flop

-

Напомним, что триггер SR работает либо с положительными тактовыми переходами, либо с отрицательными тактовыми переходами. Он имеет два входа: S и R и два выхода: Q (t) и Q (t) ‘. Выходы Q (t) и Q (t) ‘дополняют друг друга.

-

В следующей таблице показана таблица состояний SR-триггера

Напомним, что триггер SR работает либо с положительными тактовыми переходами, либо с отрицательными тактовыми переходами. Он имеет два входа: S и R и два выхода: Q (t) и Q (t) ‘. Выходы Q (t) и Q (t) ‘дополняют друг друга.

В следующей таблице показана таблица состояний SR-триггера

| S | р | Q (T + 1) |

|---|---|---|

| 0 | 0 | Q (T) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | — |

-

Здесь Q (t) и Q (t + 1) представляют собой текущее состояние и следующее состояние соответственно. Таким образом, триггер SR можно использовать для одной из этих трех функций, таких как удержание, сброс и установка, в зависимости от условий входа, когда применяется положительный (отрицательный) переход тактового сигнала.

-

Выходы нижнего компаратора (LC) и верхнего компаратора (UC) применяются как входы триггера SR, как показано на функциональной схеме 555 таймера IC.

Здесь Q (t) и Q (t + 1) представляют собой текущее состояние и следующее состояние соответственно. Таким образом, триггер SR можно использовать для одной из этих трех функций, таких как удержание, сброс и установка, в зависимости от условий входа, когда применяется положительный (отрицательный) переход тактового сигнала.

Выходы нижнего компаратора (LC) и верхнего компаратора (UC) применяются как входы триггера SR, как показано на функциональной схеме 555 таймера IC.

Транзисторы и инверторы

-

Функциональная схема 555 таймера ИС состоит из одного npn-транзистора Q1 и одного pnp-транзистора Q2. Транзистор npn Q1 будет включен, если его база к напряжению эмиттера положительна и больше, чем напряжение включения. В противном случае он будет выключен.

-

Транзистор pnp Q2 используется в качестве буфера , чтобы изолировать вход сброса от триггера SR и транзистора npn Q1.

-

Инвертор, используемый на функциональной схеме ИС таймера 555, не только выполняет инвертирующее действие, но также усиливает уровень мощности.

Функциональная схема 555 таймера ИС состоит из одного npn-транзистора Q1 и одного pnp-транзистора Q2. Транзистор npn Q1 будет включен, если его база к напряжению эмиттера положительна и больше, чем напряжение включения. В противном случае он будет выключен.

Транзистор pnp Q2 используется в качестве буфера , чтобы изолировать вход сброса от триггера SR и транзистора npn Q1.

Инвертор, используемый на функциональной схеме ИС таймера 555, не только выполняет инвертирующее действие, но также усиливает уровень мощности.

ИС таймера 555 можно использовать в моностабильном режиме для генерации импульса на выходе. Точно так же это может использоваться в нестабильной операции, чтобы произвести прямоугольную волну на выходе.