Аналого-цифровой преобразователь (АЦП) преобразует аналоговый сигнал в цифровой сигнал. Цифровой сигнал представлен двоичным кодом, который представляет собой комбинацию битов 0 и 1.

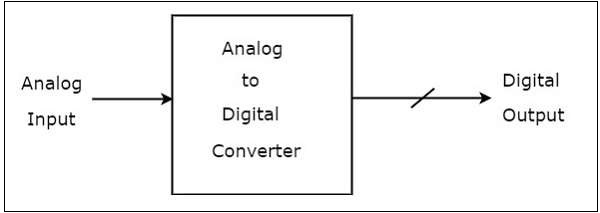

Блок-схема АЦП показана на следующем рисунке —

Обратите внимание, что на рисунке, показанном выше, аналого-цифровой преобразователь (АЦП) состоит из одного аналогового входа и множества двоичных выходов. В общем, количество двоичных выходов АЦП будет степенью двойки.

Существует два типа АЦП: АЦП прямого типа и АЦП косвенного типа. В этой главе подробно рассматриваются АЦП прямого типа.

Если АЦП выполняет аналого-цифровое преобразование напрямую, используя для сравнения с аналоговым входом внутренний сгенерированный эквивалентный (двоичный) код, то он называется АЦП прямого типа .

Ниже приведены примеры АЦП прямого типа:

- Тип счетчика АЦП

- Последовательное приближение АЦП

- Тип вспышки АЦП

В этом разделе подробно обсуждаются эти АЦП прямого типа.

Тип счетчика АЦП

АЦП типа счетчика производит цифровой выход, который приблизительно равен аналоговому входу при использовании внутреннего счетчика.

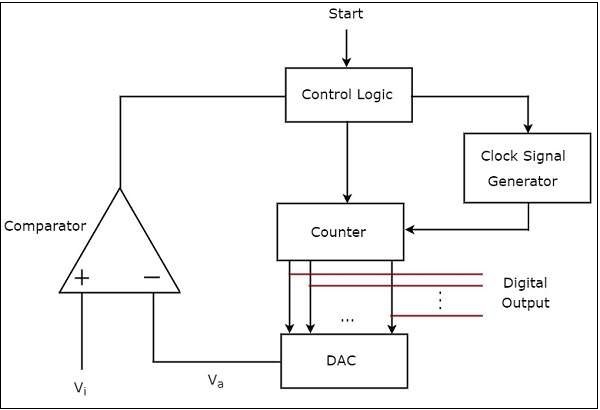

Блок-схема счетчика типа АЦП показана на следующем рисунке —

Счетчик типа АЦП в основном состоит из 5 блоков: тактового генератора, счетчика, ЦАП, компаратора и логики управления.

Работа счетчика типа АЦП заключается в следующем —

-

Логика управления сбрасывает счетчик и включает генератор тактовых сигналов, чтобы посылать тактовые импульсы на счетчик, когда он получил командный сигнал запуска.

-

Счетчик увеличивается на единицу для каждого тактового импульса, и его значение будет в двоичном (цифровом) формате. Этот выход счетчика применяется как вход ЦАП.

-

ЦАП преобразует полученный двоичный (цифровой) вход, который является выходом счетчика, в аналоговый выход. Компаратор сравнивает это аналоговое значение Va с внешним значением аналогового входа Vi.

-

Выход компаратора будет равен «1», если ?? больше, чем. Операции, упомянутые выше в двух шагах, будут продолжаться до тех пор, пока логика управления получит «1» с выхода компаратора.

-

Выход компаратора будет равен «0», когда Vi меньше или равен Va. Таким образом, управляющая логика получает «0» с выхода компаратора. Затем управляющая логика отключает генератор тактового сигнала, чтобы он не отправлял тактовый импульс на счетчик.

-

В этот момент выход счетчика будет отображаться как цифровой выход . Это почти эквивалентно соответствующему внешнему значению аналогового входа Vi.

Логика управления сбрасывает счетчик и включает генератор тактовых сигналов, чтобы посылать тактовые импульсы на счетчик, когда он получил командный сигнал запуска.

Счетчик увеличивается на единицу для каждого тактового импульса, и его значение будет в двоичном (цифровом) формате. Этот выход счетчика применяется как вход ЦАП.

ЦАП преобразует полученный двоичный (цифровой) вход, который является выходом счетчика, в аналоговый выход. Компаратор сравнивает это аналоговое значение Va с внешним значением аналогового входа Vi.

Выход компаратора будет равен «1», если ?? больше, чем. Операции, упомянутые выше в двух шагах, будут продолжаться до тех пор, пока логика управления получит «1» с выхода компаратора.

Выход компаратора будет равен «0», когда Vi меньше или равен Va. Таким образом, управляющая логика получает «0» с выхода компаратора. Затем управляющая логика отключает генератор тактового сигнала, чтобы он не отправлял тактовый импульс на счетчик.

В этот момент выход счетчика будет отображаться как цифровой выход . Это почти эквивалентно соответствующему внешнему значению аналогового входа Vi.

Последовательное приближение АЦП

АЦП типа последовательной аппроксимации производит цифровой выход, который приблизительно равен аналоговому входу, используя внутреннюю технику последовательной аппроксимации.

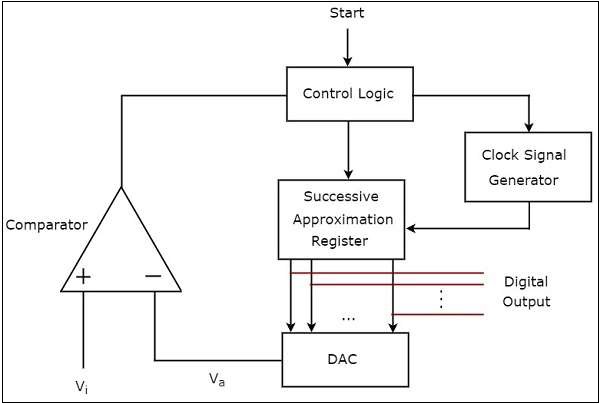

Блок-схема АЦП последовательного приближения показана на следующем рисунке

АЦП последовательного приближения в основном состоит из 5 блоков: генератор тактового сигнала, регистр последовательного приближения (SAR), ЦАП, компаратор и логика управления.

Работа АЦП последовательного приближения выглядит следующим образом —

-

Логика управления сбрасывает все биты SAR и включает генератор тактовых сигналов, чтобы посылать тактовые импульсы в SAR, когда он получил командный сигнал запуска.

-

Двоичные (цифровые) данные, присутствующие в SAR, будут обновляться для каждого тактового импульса на основе выхода компаратора. Выход SAR применяется как вход ЦАП.

-

ЦАП преобразует полученный цифровой вход, который является выходом SAR, в аналоговый выход. Компаратор сравнивает это аналоговое значение Va с внешним значением аналогового входа Vi.

-

Выходное значение компаратора будет равно «1», если Vi больше, чем Va. Точно так же выход компаратора будет равен «0», когда Vi меньше или равен Va.

-

Операции, упомянутые в вышеприведенных шагах, будут продолжаться до тех пор, пока цифровой выход не станет действительным.

Логика управления сбрасывает все биты SAR и включает генератор тактовых сигналов, чтобы посылать тактовые импульсы в SAR, когда он получил командный сигнал запуска.

Двоичные (цифровые) данные, присутствующие в SAR, будут обновляться для каждого тактового импульса на основе выхода компаратора. Выход SAR применяется как вход ЦАП.

ЦАП преобразует полученный цифровой вход, который является выходом SAR, в аналоговый выход. Компаратор сравнивает это аналоговое значение Va с внешним значением аналогового входа Vi.

Выходное значение компаратора будет равно «1», если Vi больше, чем Va. Точно так же выход компаратора будет равен «0», когда Vi меньше или равен Va.

Операции, упомянутые в вышеприведенных шагах, будут продолжаться до тех пор, пока цифровой выход не станет действительным.

Цифровой выход будет действительным, когда он почти эквивалентен соответствующему значению внешнего аналогового входа Vi.

Тип вспышки АЦП

АЦП со вспышкой производит мгновенный эквивалентный цифровой выход для соответствующего аналогового входа. Следовательно, флэш-тип АЦП является самым быстрым АЦП.

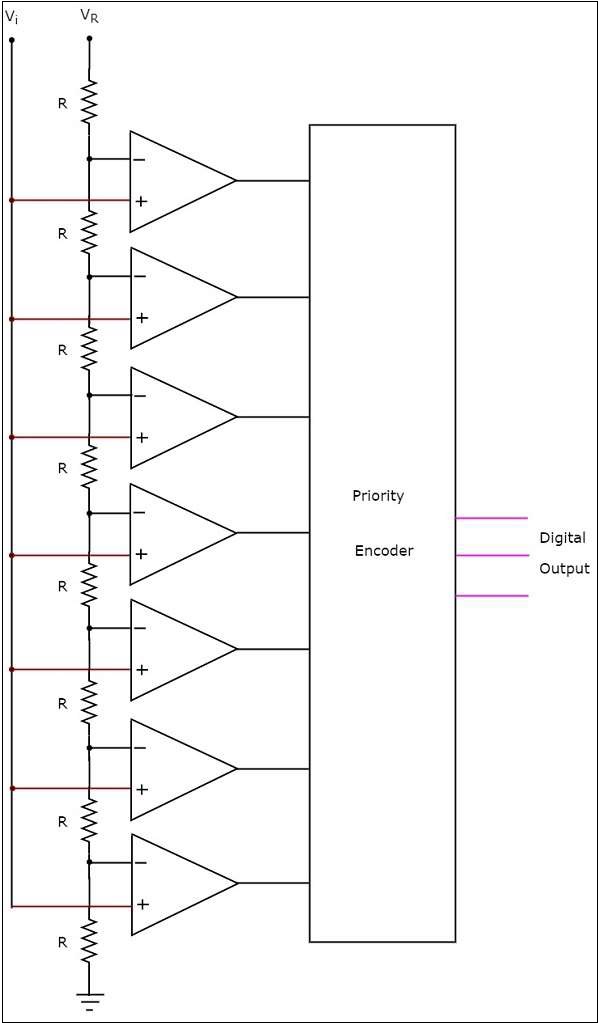

Принципиальная электрическая схема 3-разрядного АЦП со вспышкой показана на следующем рисунке.

АЦП 3-разрядного типа флэш-памяти состоит из сети делителя напряжения, 7 компараторов и датчика приоритета.

Работа 3-разрядного АЦП с флэш-памятью заключается в следующем.

-

Сеть делителей напряжения содержит 8 равных резисторов. Опорное напряжение VR прикладываются через эту всю сеть по отношению к земле. Падение напряжения на каждом резисторе снизу вверх относительно земли будет целочисленным кратным (от 1 до 8) fracVR8.

-

Внешнее входное напряжение Vi подается на неинвертирующий вывод всех компараторов. Падение напряжения на каждом резисторе снизу вверх относительно земли прикладывается к инвертирующей клемме компараторов снизу вверх.

-

Одновременно все компараторы сравнивают внешнее входное напряжение с падениями напряжения, присутствующими на соответствующей другой входной клемме. Это означает, что операции сравнения выполняются каждым компаратором параллельно .

-

Выход компаратора будет равен «1», если значение Vi больше, чем падение напряжения, присутствующее на соответствующей другой входной клемме. Аналогичным образом, выход компаратора будет равен «0», когда Vi меньше или равно падению напряжения, присутствующему на соответствующей другой входной клемме.

-

Все выходы компараторов подключены как входы приоритетного кодера. Этот приоритетный кодер выдает двоичный код (цифровой выход), который соответствует высокоприоритетному входу, имеющему «1».

-

Поэтому выходной сигнал приоритетного датчика представляет собой не что иное, как двоичный эквивалент (цифровой выход) напряжения внешнего аналогового входа, Vi.

Сеть делителей напряжения содержит 8 равных резисторов. Опорное напряжение VR прикладываются через эту всю сеть по отношению к земле. Падение напряжения на каждом резисторе снизу вверх относительно земли будет целочисленным кратным (от 1 до 8) fracVR8.

Внешнее входное напряжение Vi подается на неинвертирующий вывод всех компараторов. Падение напряжения на каждом резисторе снизу вверх относительно земли прикладывается к инвертирующей клемме компараторов снизу вверх.

Одновременно все компараторы сравнивают внешнее входное напряжение с падениями напряжения, присутствующими на соответствующей другой входной клемме. Это означает, что операции сравнения выполняются каждым компаратором параллельно .

Выход компаратора будет равен «1», если значение Vi больше, чем падение напряжения, присутствующее на соответствующей другой входной клемме. Аналогичным образом, выход компаратора будет равен «0», когда Vi меньше или равно падению напряжения, присутствующему на соответствующей другой входной клемме.

Все выходы компараторов подключены как входы приоритетного кодера. Этот приоритетный кодер выдает двоичный код (цифровой выход), который соответствует высокоприоритетному входу, имеющему «1».

Поэтому выходной сигнал приоритетного датчика представляет собой не что иное, как двоичный эквивалент (цифровой выход) напряжения внешнего аналогового входа, Vi.

АЦП со вспышкой используется в приложениях, где скорость преобразования аналогового ввода в цифровые данные должна быть очень высокой.