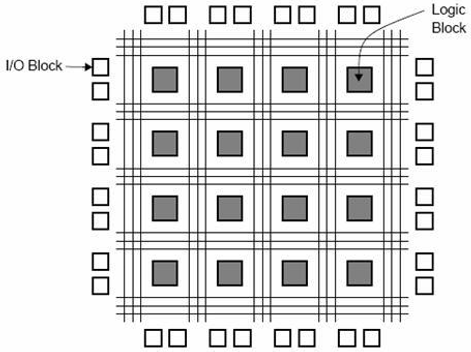

Полная форма FPGA — « Программируемый полевой массив ворот ». Он содержит от десяти тысяч до более миллиона логических элементов с программируемым соединением. Программируемые соединения доступны для пользователей или дизайнеров для легкого выполнения заданных функций. Типичная модель чипа FPGA показана на данном рисунке. Существуют блоки ввода / вывода, которые спроектированы и пронумерованы в соответствии с функцией. Для каждого модуля составления логического уровня существуют CLB (конфигурируемые логические блоки) .

CLB выполняет логическую операцию, данную модулю. Взаимосвязь между блоками CLB и I / O осуществляется с помощью горизонтальных каналов маршрутизации, вертикальных каналов маршрутизации и PSM (программируемых мультиплексоров).

Количество CLB, которое это содержит, только решает сложность FPGA. Функциональность CLB и PSM разработана VHDL или любым другим описательным языком аппаратного обеспечения. После программирования CLB и PSM размещаются на микросхеме и соединяются друг с другом каналами маршрутизации.

преимущества

- Это требует очень маленького времени; начиная от процесса проектирования до функционального чипа.

- Никакие физические производственные шаги не вовлечены в это.

- Единственный недостаток, это дороже, чем другие стили.

Gate Array Design

Массив гейта (GA) занимает второе место после FPGA с точки зрения возможности быстрого прототипирования. В то время как пользовательское программирование важно для реализации проекта чипа FPGA, дизайн GA обработки и обработки металлической маски. Реализация массива Gate требует двухэтапного производственного процесса.

Первая фаза приводит к массиву незафиксированных транзисторов на каждом чипе GA. Эти незафиксированные микросхемы могут быть сохранены для последующей настройки, которая завершается определением металлических межсоединений между транзисторами массива. Моделирование металлических межсоединений выполняется в конце процесса изготовления микросхемы, поэтому время оборота может быть коротким, от нескольких дней до нескольких недель. На приведенном ниже рисунке показаны основные этапы обработки для реализации массива гейтов.

Типичные платформы массива затворов используют выделенные области, называемые каналами, для межклеточной маршрутизации между строками или столбцами MOS-транзисторов. Они упрощают взаимосвязи. Шаблоны соединений, которые выполняют базовые логические элементы, хранятся в библиотеке, которую затем можно использовать для настройки рядов незафиксированных транзисторов в соответствии с сетевым списком.

В большинстве современных GA для маршрутизации каналов используются несколько металлических слоев. С использованием нескольких взаимосвязанных уровней маршрутизация может быть достигнута по активным областям соты; так что каналы маршрутизации могут быть удалены как в чипах Sea-of-Gates (SOG). Здесь вся поверхность чипа покрыта незафиксированными транзисторами nMOS и pMOS. Соседние транзисторы могут быть настроены с использованием металлической маски для формирования базовых логических элементов.

Для межсотовой маршрутизации некоторые из незафиксированных транзисторов должны быть принесены в жертву. Этот стиль дизайна обеспечивает большую гибкость для соединений и, как правило, более высокую плотность. Коэффициент использования микросхемы GA измеряется по площади использованной микросхемы, деленной на общую площадь микросхемы. Это выше, чем у FPGA, и поэтому скорость чипа.

Стандартный сотовый дизайн

Стандартный дизайн на основе ячеек требует разработки полного пользовательского набора масок. Стандартная клетка также известна как полицелл. При таком подходе все обычно используемые логические ячейки разрабатываются, характеризуются и хранятся в стандартной библиотеке ячеек.

Библиотека может содержать несколько сотен ячеек, включая инверторы, вентили NAND, вентили NOR, сложные AOI, вентили OAI, D-защелки и триггеры. Каждый тип ворот может быть реализован в нескольких версиях, чтобы обеспечить адекватные возможности вождения для различных разветвлений. Вентиль инвертора может иметь стандартный размер, двойной размер и четырехкратный размер, так что разработчик микросхемы может выбрать правильный размер для получения высокой скорости цепи и плотности компоновки.

Каждая ячейка характеризуется в соответствии с несколькими различными категориями характеристик, такими как,

- Время задержки в зависимости от емкости нагрузки

- Имитационная модель цепи

- Временная имитационная модель

- Имитационная модель неисправности

- Данные ячейки для места и маршрута

- Маска данных

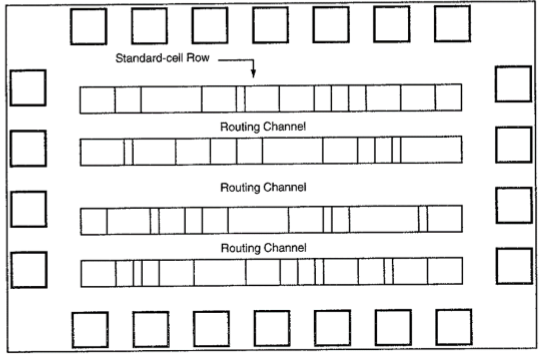

Для автоматического размещения ячеек и маршрутизации каждая разметка ячеек имеет фиксированную высоту, так что несколько ячеек могут быть связаны бок о бок для образования рядов. Силовые и заземляющие рельсы проходят параллельно верхней и нижней границам ячейки. Таким образом, соседние ячейки имеют общую шину питания и общую шину заземления. На рисунке ниже приведен план этажа для дизайна на основе стандартных ячеек.

Полный индивидуальный дизайн

В полностью индивидуальном дизайне весь дизайн маски сделан новым, без использования какой-либо библиотеки. Стоимость разработки этого стиля дизайна растет. Таким образом, концепция повторного использования дизайна становится известной, чтобы сократить время цикла проектирования и стоимость разработки.

Самым сложным полностью индивидуальным дизайном может быть дизайн ячейки памяти, будь то статический или динамический. Для проектирования логического чипа хорошее согласование может быть получено с использованием комбинации разных стилей проектирования на одном чипе, то есть стандартных ячеек, ячеек тракта данных и программируемых логических массивов (PLA) .

Практически, дизайнер делает полную пользовательскую компоновку, то есть геометрию, ориентацию и размещение каждого транзистора. Производительность проектирования обычно очень низкая; как правило, несколько десятков транзисторов в день на дизайнера. В цифровых CMOS VLSI, полностью индивидуальный дизайн практически не используется из-за высокой стоимости рабочей силы. Эти стили дизайна включают в себя разработку продуктов большого объема, таких как микросхемы памяти, высокопроизводительные микропроцессоры и FPGA.