СБИС Дизайн — Цифровая система

Очень крупномасштабная интеграция (VLSI) — это процесс создания интегральной схемы (ИС) путем объединения тысяч транзисторов в один чип. СБИС началось в 1970-х годах, когда разрабатывались сложные полупроводниковые и коммуникационные технологии. Микропроцессор является устройством VLSI.

До внедрения технологии VLSI большинство микросхем имели ограниченный набор функций, которые они могли выполнять. Электронная схема может состоять из процессора, ПЗУ, ОЗУ и другой связующей логики . VLSI позволяет разработчикам интегральных схем добавить все это в один чип.

Электронная промышленность достигла феноменального роста за последние несколько десятилетий, главным образом благодаря быстрому прогрессу в области крупномасштабных интеграционных технологий и приложений для проектирования систем. С появлением проектов очень крупномасштабной интеграции (VLSI) число применений интегральных микросхем (ИС) в высокопроизводительных вычислениях, средствах управления, телекоммуникациях, обработке изображений и видео, а также бытовой электронике растет очень быстрыми темпами.

Современные передовые технологии, такие как видео и сотовая связь с высоким разрешением и низкой скоростью передачи битов, обеспечивают конечным пользователям изумительное количество приложений, вычислительную мощность и мобильность. Ожидается, что эта тенденция будет быстро развиваться, что будет иметь очень важное значение для проектирования СБИС и систем.

VLSI Design Flow

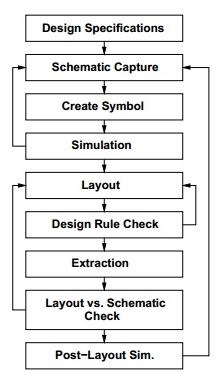

Схема проектирования микросхем СБИС показана на рисунке ниже. Различные уровни дизайна пронумерованы, и блоки показывают процессы в процессе проектирования.

Сначала идут спецификации, они описывают абстрактно, функциональность, интерфейс и архитектуру цифровой схемы IC, которая будет разработана.

Затем создается поведенческое описание для анализа дизайна с точки зрения функциональности, производительности, соответствия заданным стандартам и других спецификаций.

Описание RTL выполняется с использованием HDL. Это описание RTL моделируется для проверки функциональности. С этого момента нам нужна помощь инструментов EDA.

Затем описание RTL преобразуется в список соединений уровня шлюза с использованием инструментов логического синтеза. Список соединений уровня шлюза — это описание схемы в терминах затворов и соединений между ними, которые выполнены таким образом, что они соответствуют характеристикам синхронизации, мощности и площади.

Наконец, создается физический макет, который будет проверен и затем отправлен на изготовление.

Y Диаграмма

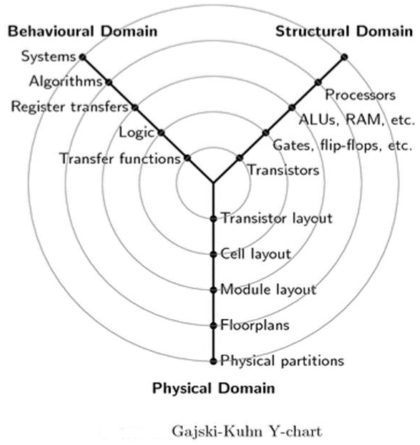

Y-диаграмма Гайски-Куна — это модель, которая учитывает соображения при разработке полупроводниковых приборов.

Три области Y-диаграммы Гайски-Куна находятся на радиальных осях. Каждый из доменов можно разделить на уровни абстракции, используя концентрические кольца.

На верхнем уровне (внешнее кольцо) мы рассмотрим архитектуру чипа; на нижних уровнях (внутренние кольца) мы последовательно совершенствуем проект до более детальной реализации —

Создание структурного описания из поведенческого достигается посредством процессов синтеза высокого уровня или логического синтеза.

Создание физического описания из структурного достигается путем синтеза макета.

Иерархия проектирования — Структурная

Иерархия дизайна включает в себя принцип «Разделяй и властвуй». Это не что иное, как деление задачи на более мелкие задачи, пока она не достигнет своего простейшего уровня. Этот процесс является наиболее подходящим, потому что последнее развитие дизайна стало настолько простым, что его изготовление стало легче.

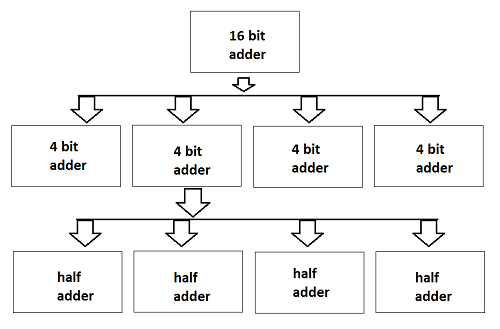

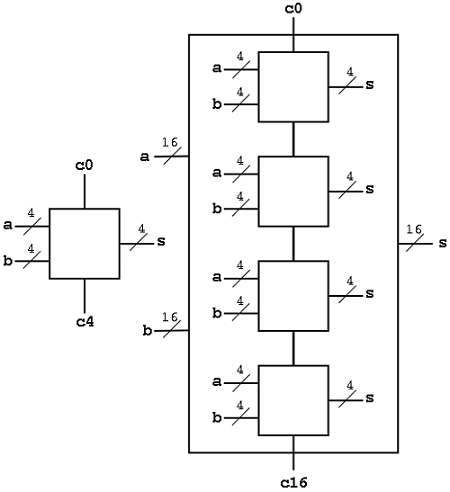

Мы можем спроектировать данную задачу в область процесса проектирования (Поведенческий, Структурный и Геометрический). Чтобы понять это, давайте рассмотрим пример проектирования 16-разрядного сумматора, как показано на рисунке ниже.

Здесь весь чип 16-битного сумматора разделен на четыре модуля 4-битных сумматоров. Далее делим 4-битный сумматор на 1-битный сумматор или половину сумматора. Добавление 1 бита является самым простым процессом проектирования, и его внутреннюю схему также легко изготовить на чипе. Теперь, соединив все последние четыре сумматора, мы можем спроектировать 4-битный сумматор и, двигаясь дальше, мы можем спроектировать 16-битный сумматор.

VLSI Design — технология FPGA

FPGA — Введение

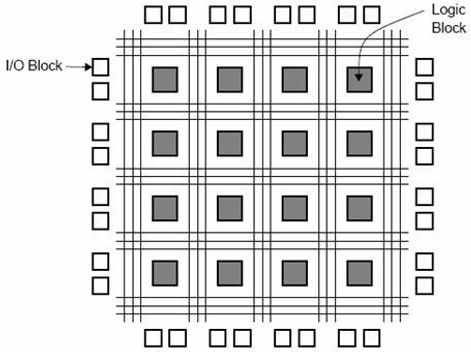

Полная форма FPGA — « Программируемый полевой массив ворот ». Он содержит от десяти тысяч до более миллиона логических элементов с программируемым соединением. Программируемые соединения доступны для пользователей или дизайнеров для легкого выполнения заданных функций. Типичная модель чипа FPGA показана на данном рисунке. Существуют блоки ввода / вывода, которые спроектированы и пронумерованы в соответствии с функцией. Для каждого модуля составления логического уровня существуют CLB (конфигурируемые логические блоки) .

CLB выполняет логическую операцию, данную модулю. Взаимосвязь между блоками CLB и I / O осуществляется с помощью горизонтальных каналов маршрутизации, вертикальных каналов маршрутизации и PSM (программируемых мультиплексоров).

Количество CLB, которое это содержит, только решает сложность FPGA. Функциональность CLB и PSM разработана VHDL или любым другим описательным языком аппаратного обеспечения. После программирования CLB и PSM размещаются на микросхеме и соединяются друг с другом каналами маршрутизации.

преимущества

- Это требует очень маленького времени; начиная от процесса проектирования до функционального чипа.

- Никакие физические производственные шаги не вовлечены в это.

- Единственный недостаток, это дороже, чем другие стили.

Gate Array Design

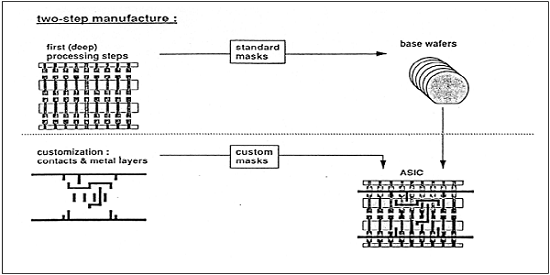

Массив гейта (GA) занимает второе место после FPGA с точки зрения возможности быстрого прототипирования. В то время как пользовательское программирование важно для реализации проекта чипа FPGA, дизайн GA обработки и обработки металлической маски. Реализация массива Gate требует двухэтапного производственного процесса.

Первая фаза приводит к массиву незафиксированных транзисторов на каждом чипе GA. Эти незафиксированные микросхемы могут быть сохранены для последующей настройки, которая завершается определением металлических межсоединений между транзисторами массива. Моделирование металлических межсоединений выполняется в конце процесса изготовления микросхемы, поэтому время оборота может быть коротким, от нескольких дней до нескольких недель. На приведенном ниже рисунке показаны основные этапы обработки для реализации массива гейтов.

Типичные платформы массива затворов используют выделенные области, называемые каналами, для межклеточной маршрутизации между строками или столбцами MOS-транзисторов. Они упрощают взаимосвязи. Шаблоны соединений, которые выполняют базовые логические элементы, хранятся в библиотеке, которую затем можно использовать для настройки рядов незафиксированных транзисторов в соответствии с сетевым списком.

В большинстве современных GA для маршрутизации каналов используются несколько металлических слоев. С использованием нескольких взаимосвязанных уровней маршрутизация может быть достигнута по активным областям соты; так что каналы маршрутизации могут быть удалены как в чипах Sea-of-Gates (SOG). Здесь вся поверхность чипа покрыта незафиксированными транзисторами nMOS и pMOS. Соседние транзисторы могут быть настроены с использованием металлической маски для формирования базовых логических элементов.

Для межсотовой маршрутизации некоторые из незафиксированных транзисторов должны быть принесены в жертву. Этот стиль дизайна обеспечивает большую гибкость для соединений и, как правило, более высокую плотность. Коэффициент использования микросхемы GA измеряется по площади использованной микросхемы, деленной на общую площадь микросхемы. Это выше, чем у FPGA, и поэтому скорость чипа.

Стандартный сотовый дизайн

Стандартный дизайн на основе ячеек требует разработки полного пользовательского набора масок. Стандартная клетка также известна как полицелл. При таком подходе все обычно используемые логические ячейки разрабатываются, характеризуются и хранятся в стандартной библиотеке ячеек.

Библиотека может содержать несколько сотен ячеек, включая инверторы, вентили NAND, вентили NOR, сложные AOI, вентили OAI, D-защелки и триггеры. Каждый тип ворот может быть реализован в нескольких версиях, чтобы обеспечить адекватные возможности вождения для различных разветвлений. Вентиль инвертора может иметь стандартный размер, двойной размер и четырехкратный размер, так что разработчик микросхемы может выбрать правильный размер для получения высокой скорости цепи и плотности компоновки.

Каждая ячейка характеризуется в соответствии с несколькими различными категориями характеристик, такими как,

- Время задержки в зависимости от емкости нагрузки

- Имитационная модель цепи

- Временная имитационная модель

- Имитационная модель неисправности

- Данные ячейки для места и маршрута

- Маска данных

Для автоматического размещения ячеек и маршрутизации каждая разметка ячеек имеет фиксированную высоту, так что несколько ячеек могут быть связаны бок о бок для образования рядов. Силовые и заземляющие рельсы проходят параллельно верхней и нижней границам ячейки. Таким образом, соседние ячейки имеют общую шину питания и общую шину заземления. На рисунке ниже приведен план этажа для дизайна на основе стандартных ячеек.

Полный индивидуальный дизайн

В полностью индивидуальном дизайне весь дизайн маски сделан новым, без использования какой-либо библиотеки. Стоимость разработки этого стиля дизайна растет. Таким образом, концепция повторного использования дизайна становится известной, чтобы сократить время цикла проектирования и стоимость разработки.

Самым сложным полностью индивидуальным дизайном может быть дизайн ячейки памяти, будь то статический или динамический. Для проектирования логического чипа хорошее согласование может быть получено с использованием комбинации разных стилей проектирования на одном чипе, то есть стандартных ячеек, ячеек тракта данных и программируемых логических массивов (PLA) .

Практически, дизайнер делает полную пользовательскую компоновку, то есть геометрию, ориентацию и размещение каждого транзистора. Производительность проектирования обычно очень низкая; как правило, несколько десятков транзисторов в день на дизайнера. В цифровых CMOS VLSI, полностью индивидуальный дизайн практически не используется из-за высокой стоимости рабочей силы. Эти стили дизайна включают в себя разработку продуктов большого объема, таких как микросхемы памяти, высокопроизводительные микропроцессоры и FPGA.

VLSI Design — МОП-транзистор

Комплементарная технология MOSFET (CMOS) широко используется сегодня для формирования схем в многочисленных и разнообразных приложениях. Современные компьютеры, процессоры и мобильные телефоны используют CMOS из-за нескольких ключевых преимуществ. CMOS предлагает низкое рассеивание мощности, относительно высокую скорость, высокие запасы шума в обоих состояниях и будет работать в широком диапазоне напряжений источника и входа (при условии, что напряжение источника фиксировано)

Для процессов, которые мы обсудим, тип доступного транзистора — полевой транзистор металл-оксид-полупроводник (MOSFET). Эти транзисторы сформированы в виде «сэндвича», состоящего из полупроводникового слоя, обычно среза или пластины, из монокристалла кремния; слой диоксида кремния (оксид) и слой металла.

Структура МОП-транзистора

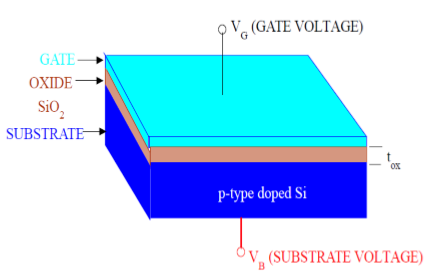

Как показано на рисунке, структура MOS содержит три слоя:

-

Металлические ворота Электрод

-

Изолирующий оксидный слой (SiO 2 )

-

Полупроводник типа P (подложка)

Металлические ворота Электрод

Изолирующий оксидный слой (SiO 2 )

Полупроводник типа P (подложка)

МОП-структура образует конденсатор, причем затвор и подложка выполнены в виде двух пластин, а оксидный слой — как диэлектрический материал. Толщина диэлектрического материала (SiO 2 ) обычно составляет от 10 нм до 50 нм. Концентрацией и распределением носителей внутри подложки можно управлять с помощью внешнего напряжения, прикладываемого к затвору и клемме подложки. Теперь, чтобы понять структуру МОП, сначала рассмотрим основные электрические свойства полупроводниковой подложки P-типа.

Концентрация носителя в полупроводниковом материале всегда следует закону массового действия . Закон о массовых действиях дан

нп=П−я2

Куда,

-

n — концентрация носителей электронов

-

р — концентрация носителей дырок

-

n i — собственная концентрация носителей кремния

n — концентрация носителей электронов

р — концентрация носителей дырок

n i — собственная концентрация носителей кремния

Теперь предположим, что субстрат в равной степени легирован акцепторной (борной) концентрацией N A. Таким образом, концентрация электронов и дырок в подложке p-типа

nро= гидроразрываn2яNA

р−ро=NA,

Здесь концентрация легирования N A (от 10 15 до 10 16 см -3 ) больше, чем собственная концентрация ni. Теперь, чтобы понять структуру МОП, рассмотрим диаграмму энергетических уровней кремниевой подложки p-типа.

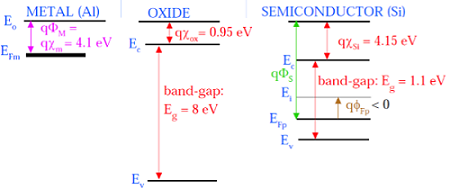

Как показано на рисунке, ширина запрещенной зоны между зоной проводимости и валансной зоной составляет 1,1 эВ. Здесь потенциал Ферми Φ F представляет собой разность между собственным уровнем Ферми (E i ) и уровнем Ферми (E FP ).

Где уровень Ферми E F зависит от концентрации легирования. Потенциал Ферми Φ F представляет собой разность между собственным уровнем Ферми (E i ) и уровнем Ферми (E FP ).

Математически,

PhiFp= гидроразрываЕ−F−Eяд

Разность потенциалов между зоной проводимости и свободным пространством называется сродством к электрону и обозначается через qx.

Таким образом, энергия, необходимая для перехода электрона с уровня Ферми в свободное пространство, называется работой выхода (qΦ S ) и определяется как

q Phis=(Ec−EF)+qx

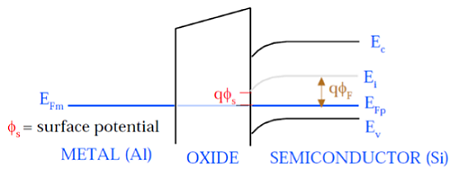

На следующем рисунке показана диаграмма энергетических зон компонентов, из которых состоит МОП.

Как показано на приведенном выше рисунке, изолирующий слой SiO 2 имеет большую запрещенную зону энергии, равную 8 эВ, и работу выхода составляет 0,95 эВ. Металлические ворота имеют рабочую функцию 4,1 эВ. Здесь рабочие функции отличаются, поэтому это приведет к падению напряжения в системе MOS. На приведенном ниже рисунке показана объединенная диаграмма энергетических зон системы MOS.

Как показано на этом рисунке, уровень ферми-потенциала металлического затвора и полупроводника (Si) находятся на одном потенциале. Потенциал Ферми на поверхности называется поверхностным потенциалом Φ S, и он меньше, чем потенциал Ферми Φ F по величине.

Рабочая МОП-транзистор

МОП-транзистор состоит из МОП-конденсатора с двумя pn-переходами, расположенными закрытыми в области канала, и эта область контролируется напряжением затвора. Для того чтобы оба pn-перехода были смещены в обратном направлении, потенциал подложки поддерживается ниже, чем потенциал трех других клемм.

Если напряжение затвора будет увеличено сверх порогового напряжения (V GS > V TO ), на поверхности будет создан инверсионный слой и между истоком и стоком будет сформирован канал n-типа. Этот канал n-типа будет передавать ток стока в соответствии со значением V DS .

Для разных значений V DS МОП-транзистор может работать в разных регионах, как описано ниже.

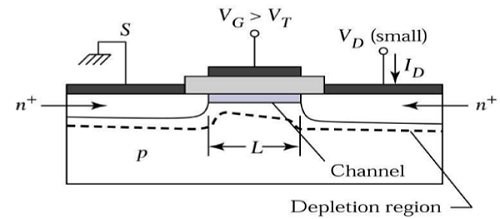

Линейный регион

При V DS = 0 в области инвертированного канала существует тепловое равновесие и ток стока I D = 0. Теперь, если приложено небольшое напряжение стока, V DS > 0, ток стока, пропорциональный V DS , начнет течь от источника к слить через канал.

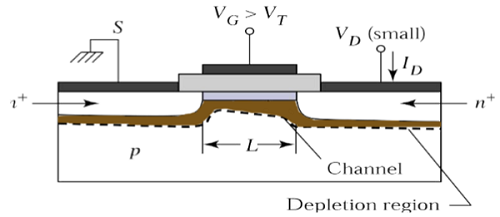

Канал дает непрерывный путь для протекания тока от источника к стоку. Этот режим работы называется линейной областью . Вид в поперечном сечении n-канального полевого МОП-транзистора, работающего в линейной области, показан на рисунке ниже.

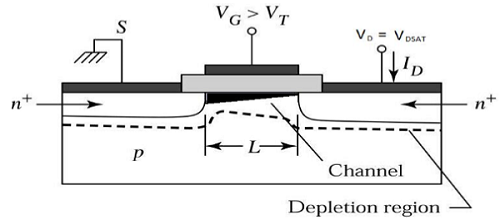

На краю области насыщения

Теперь, если V DS увеличивается, заряды в канале и глубина канала уменьшаются в конце стока. Для V DS = V DSAT расходы в канале уменьшаются до нуля, что называется точкой отсечки . Вид в поперечном сечении n-канального полевого МОП-транзистора, работающего на краю области насыщения, показан на рисунке, приведенном ниже.

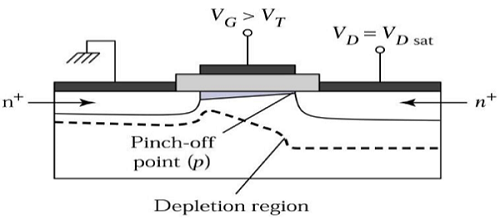

Регион насыщенности

Для V DS > V DSAT , истощенная поверхность образуется вблизи стока, и при увеличении напряжения стока эта обедненная область распространяется на исток.

Этот режим работы называется областью насыщения . Электроны, поступающие от истока к концу канала, попадают в область истощения и ускоряются в направлении стока в сильном электрическом поле.

МОП-транзистор Ток — Характеристики напряжения

Чтобы понять вольт-амперную характеристику МОП-транзистора, выполняется аппроксимация для канала. Без этого приближения трехмерный анализ системы MOS становится сложным. Постепенное приближение канала (GCA) для вольт-амперной характеристики уменьшит проблему анализа.

Постепенная аппроксимация канала (GCA)

Рассмотрим поперечное сечение n-канального полевого МОП-транзистора, работающего в линейном режиме. Здесь источник и подложка связаны с землей. V S = V B = 0. Напряжение затвор-исток (V GS ) и напряжение сток-исток (V DS ) являются внешними параметрами, управляющими током стока I D.

Напряжение V GS устанавливается на напряжение, превышающее пороговое напряжение V TO , для создания канала между истоком и стоком. Как показано на рисунке, направление x перпендикулярно поверхности, а направление y параллельно поверхности.

Здесь y = 0 в конце источника, как показано на рисунке. Напряжение на канале относительно источника представлено как V C (Y) . Предположим, что пороговое напряжение VTO является постоянным вдоль области канала, от y = 0 до y = L. Граничные условия для напряжения V C канала составляют —

Vc left(y=0 right)=Vs=0 иVc left(y=L right)=VDS

Мы также можем предположить, что

VGS geqVTO и

VGD=VGS−VDS geqVTO

Пусть Q1 (y) — полный заряд мобильного электрона в поверхностном инверсионном слое. Этот электронный заряд может быть выражен как —

Q1(у)=−Cвола[VГ.С.−VC(Y)−VК].

На приведенном ниже рисунке показана пространственная геометрия поверхностного инверсионного слоя и указаны его размеры. Инверсионный слой сужается, когда мы движемся от стока к источнику. Теперь, если мы рассмотрим небольшую область dy длины канала L, то добавочное сопротивление dR, предлагаемое этой областью, можно выразить как —

dR=− fracdyw. mun.Q1(y)

Здесь знак минус обусловлен отрицательной полярностью заряда инверсионного слоя Q1, а µ n — подвижность поверхности, которая постоянна. Теперь подставим значение Q1 (y) в уравнение dR —

dR = — \ frac {dy} {w. \ mu _ {n}. \ left \ {-C_ {ox} \ left [V_ {GS} -V_ {C \ left (Y \ right)} \ right ] -V_ {TO} \ right \}}

dR= fracdyw. mun.Cox left[VGS−VC left(Y right) right]−VTO

Теперь падение напряжения в небольшой области DY может быть дано

dVC=ID.dr

Поместите значение dR в приведенное выше уравнение

dVC=ID. fracdyw. mun.Cox left[VGS−VC(Y) right]−VК

w. mun.Cox left[VGS−VC(Y)−VTO right].dVC=ID.dy

Для получения идентификатора тока стока по всей области канала вышеприведенное уравнение может быть интегрировано вдоль канала от y = 0 до y = L и напряжениях V C (y) = от 0 до V C (y) = V DS ,

Cox.w. Mun. IntVDSVc=0 left[VGS−VC left(Y right))−VTO right].dVC= intLY=0ID.dy

fracCox.w. mun2 left(2 left[VGS−VTO right]VDS−V2DS right)=ID left[L−0 right]

ID= fracCox. Mun2. FracwL left(2 left[VGS−VTO right]VDS−V2DS right)

Для линейной области V DS <V GS — V TO . Для области насыщения значение V DS больше, чем (V GS — V TO ). Следовательно, для области насыщения V DS = (V GS — V К ).

ID=Cox. Mun. Fracw2 left( frac left[2VDS right]VDS−V2DSL right)

ID=Cox. Mun. Fracw2 left( frac2V2DS−V2DSL right)

ID=Cox. Mun. Fracw2 left( fracV2DSL right)

ID=Cox. Mun. Fracw2 left( frac left[VGS−VTO right]2L right)

VLSI Design — MOS Инвертор

Инвертор действительно ядро всех цифровых конструкций. Как только его работа и свойства будут понятны, проектирование более сложных структур, таких как вентили NAND, сумматоры, умножители и микропроцессоры, значительно упрощается. Электрическое поведение этих сложных цепей может быть почти полностью получено путем экстраполяции результатов, полученных для инверторов.

Анализ инверторов может быть расширен, чтобы объяснить поведение более сложных вентилей, таких как NAND, NOR или XOR, которые, в свою очередь, образуют строительные блоки для таких модулей, как умножители и процессоры. В этой главе мы сконцентрируемся на одном воплощении инверторного затвора, то есть статического КМОП-преобразователя или, вкратце, КМОП-преобразователя. Это, безусловно, самая популярная в настоящее время и поэтому заслуживает нашего особого внимания.

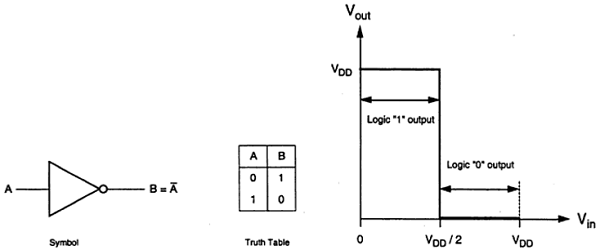

Принцип действия

Логический символ и таблица истинности идеального инвертора показаны на рисунке ниже. Здесь A является входом, а B является инвертированным выходом, представленным их узловыми напряжениями. Используя положительную логику, логическое значение логики 1 представлено V dd, а логика 0 — 0. V th — пороговое напряжение инвертора, которое равно V dd / 2, где V dd — выходное напряжение.

Выход переключается с 0 на V dd, когда вход меньше V th . Таким образом, для 0 <V на <V- ом выходе равно входу логического 0, а V th <V на <V dd равно входу логики 1 для инвертора.

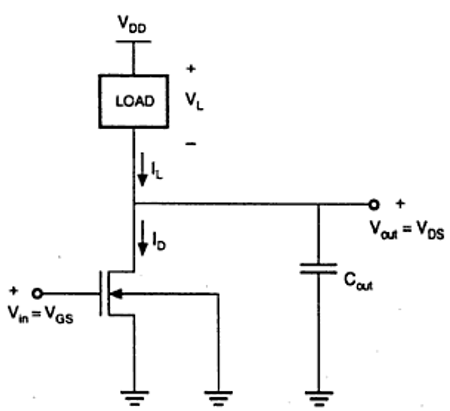

Характеристики, показанные на рисунке, идеальны. Обобщенная структура схемы инвертора nMOS показана на рисунке ниже.

Из приведенного рисунка видно, что входное напряжение инвертора равно напряжению затвора на исток nMOS-транзистора, а выходное напряжение инвертора равно напряжению на выходе истока nMOS-транзистора. Напряжение между источником и подложкой nMOS также называется драйвером для транзистора, который заземлен; поэтому V SS = 0. Выходной узел связан с сосредоточенной емкостью, используемой для VTC.

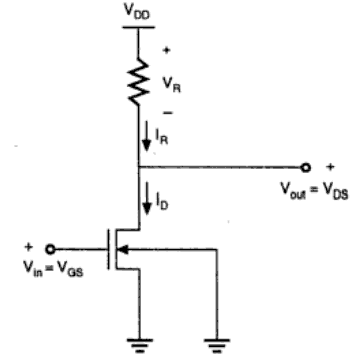

Инвертор резистивной нагрузки

Базовая структура инвертора резистивной нагрузки показана на рисунке ниже. Здесь тип расширения nMOS действует как транзистор драйвера. Нагрузка состоит из простого линейного резистора R L. Питание схемы V DD, а ток стока I D равен току нагрузки I R.

Схема работы

Когда вход транзистора возбуждения меньше порогового напряжения V TH (V в <V TH ), транзистор возбуждения находится в области среза и не проводит никакого тока. Таким образом, падение напряжения на нагрузочном резисторе равно нулю, а выходное напряжение равно V DD . Теперь, когда входное напряжение еще больше возрастает, транзистор драйвера начнет проводить ненулевой ток, и nMOS перейдет в область насыщения.

Математически,

ID= fracKn2 left[VGS−VTO right]2

При дальнейшем увеличении входного напряжения транзистор драйвера войдет в линейную область, и выходной транзистор драйвера уменьшится.

ID= fracKn22 left[VGS−VTO right]VDS−V2DS

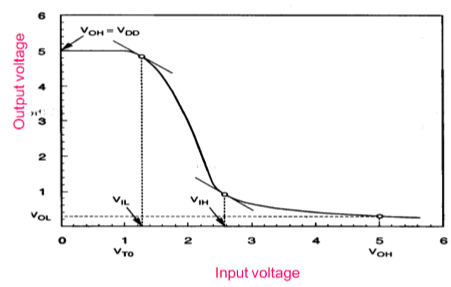

Показатель VTC резистивного нагрузочного преобразователя, показанный ниже, указывает режим работы транзистора драйвера и точки напряжения.

Инвертор с нагрузкой MOSFET типа N

Основное преимущество использования MOSFET в качестве устройства нагрузки состоит в том, что кремниевая область, занимаемая транзистором, меньше, чем площадь, занимаемая резистивной нагрузкой. Здесь MOSFET является активной нагрузкой, а инвертор с активной нагрузкой дает лучшую производительность, чем инвертор с резистивной нагрузкой.

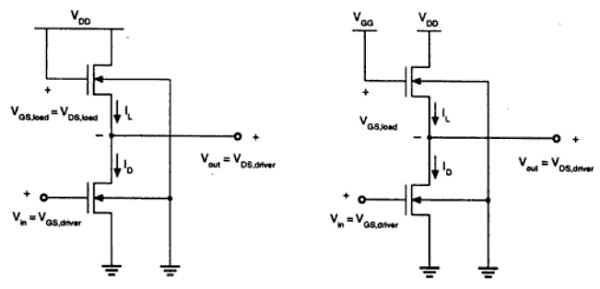

Увеличение нагрузки NMOS

Два инвертора с нагрузочным устройством улучшенного типа показаны на рисунке. Нагрузочный транзистор может работать либо в области насыщения, либо в линейной области, в зависимости от напряжения смещения, приложенного к его клемме затвора. Инвертор нагрузки с насыщенным повышением показан на рис. (А). Это требует единого источника питания и простого процесса изготовления, поэтому V OH ограничивается V DD — V T.

Линейный повышающий преобразователь нагрузки показан на рис. (Б). Он всегда работает в линейной области; поэтому уровень V OH равен V DD .

Линейный инвертор нагрузки имеет более высокий запас по сравнению с инвертором с насыщенным усилением. Но недостаток инвертора линейного усиления заключается в том, что он требует двух отдельных источников питания, и обе схемы страдают от высокого рассеивания мощности. Поэтому инверторы повышения качества не используются ни в каких крупных цифровых приложениях.

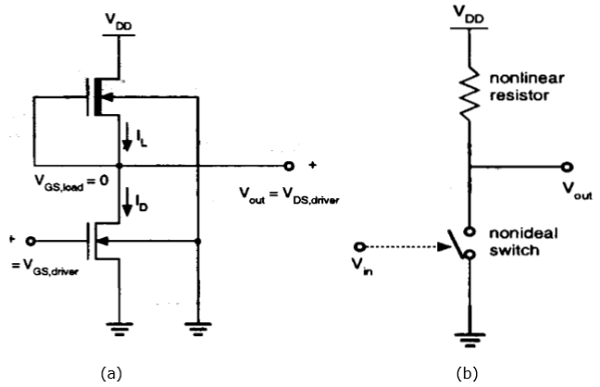

Истощение нагрузки NMOS

Недостатки повышающего инвертора нагрузки могут быть преодолены с помощью инвертора с понижающей нагрузкой. По сравнению с повышающим преобразователем нагрузки преобразователь истощающей нагрузки требует несколько дополнительных этапов изготовления канального имплантата для регулировки порогового напряжения нагрузки.

Преимущества инвертора с понижающей нагрузкой — резкий переход VTC, лучший запас шума, одиночный источник питания и меньшая общая площадь компоновки.

Как показано на рисунке, затвор и терминал нагрузки нагрузки соединены; Итак, V GS = 0. Таким образом, пороговое напряжение нагрузки является отрицательным. Следовательно,

VGS,load>VT,load выполнено

Следовательно, нагрузочное устройство всегда имеет проводящий канал независимо от уровня входного и выходного напряжения.

Когда транзистор нагрузки находится в области насыщения, ток нагрузки определяется как

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [-V_ {T, load} \ left (V_ {out} \ right) \ right] ^ {2} $ $

Когда транзистор нагрузки находится в линейной области, ток нагрузки определяется как

$$ I_ {D, загрузка} = \ frac {K_ {n, загрузка}} {2} \ left [2 \ left | V_ {T, загрузка} \ left (V_ {out} \ right) \ right |. \ Left (V_ {DD} -V_ {out} \ right) — \ left (V_ {DD} -V_ {out} \ right ) ^ {2} \ right] $$

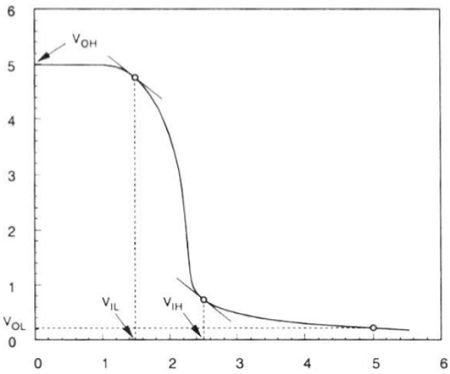

Характеристики передачи напряжения инвертора обедненной нагрузки показаны на рисунке ниже —

КМОП инвертор — схема, работа и описание

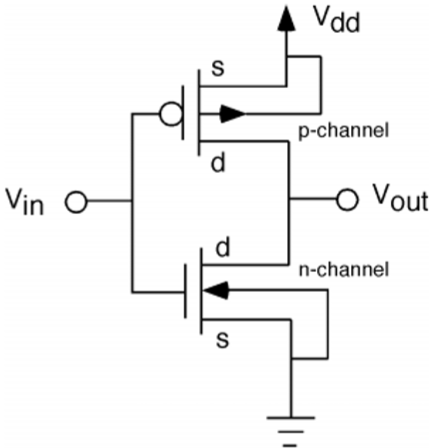

Схема инвертора CMOS показана на рисунке. Здесь транзисторы nMOS и pMOS работают как транзисторы драйвера; когда один транзистор включен, другой выключен.

Эта конфигурация называется дополнительной MOS (CMOS) . Вход подключен к клемме затвора обоих транзисторов, так что оба могут управляться напрямую с входными напряжениями. Подложка nMOS подключена к земле, а подложка pMOS подключена к источнику питания, V DD .

Таким образом, V SB = 0 для обоих транзисторов.

VГ.С.,п=Vв

VDS,п=Vиз

А также,

VГ.С.,р=Vв−VDD

VDS,р=Vиз−VDD

Когда вход nMOS меньше порогового напряжения (V в <V TO, n ), nMOS отключается, а pMOS находится в линейной области. Таким образом, ток утечки обоих транзисторов равен нулю.

ID,N=ID,P=0

Следовательно, выходное напряжение V OH равно напряжению питания.

Vиз=VОН=VДД

Когда входное напряжение больше, чем V DD + V TO, p , транзистор pMOS находится в области отсечки, а nMOS — в линейной области, поэтому ток стока обоих транзисторов равен нулю.

ID,N=ID,P=0

Следовательно, выходное напряжение V OL равно нулю.

Vиз=VOL=0

NMOS работает в области насыщения, если V in > V TO и если выполняются следующие условия.

VDS,n geqVGS,n−VTO,n

Vout geqVin−VTO,n

PMOS работает в области насыщения, если V в <V DD + V TO, p и если выполняются следующие условия.

VDS,p leqVGS,p−VTO,p

Vout leqVin−VTO,p

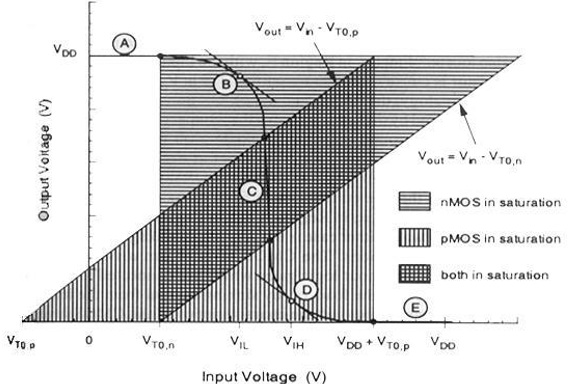

Для разных значений входных напряжений рабочие области перечислены ниже для обоих транзисторов.

| Область, край | V в | V out | NMOS | PMOS |

|---|---|---|---|---|

| <V TO, n | V OH | Отрезать | линейный | |

| В | V IL | Высокая ≈ V OH | насыщение | линейный |

| С | V й | V й | насыщение | насыщение |

| D | V IH | Низкая ≈ V OL | линейный | насыщение |

| Е | > (V DD + V TO, р ) | V OL | линейный | Отрезать |

VTC CMOS показан на рисунке ниже —

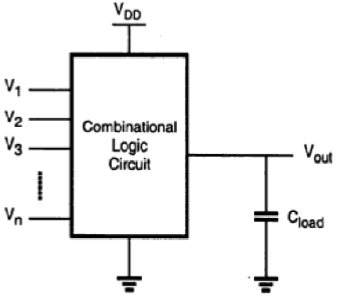

Комбинационные логические схемы MOS

Комбинационные логические схемы или логические схемы, которые выполняют логические операции с несколькими входными переменными и определяют выходы как булевы функции входов, являются основными строительными блоками всех цифровых систем. Мы рассмотрим простые конфигурации схем, такие как вентили NAND и NOR с двумя входами, а затем расширим наш анализ до более общих случаев структур с несколькими входами.

Далее логические схемы CMOS будут представлены аналогичным образом. Мы подчеркнем сходства и различия между логикой истощения нагрузки nMOS и логическими схемами CMOS и укажем на преимущества вентилей CMOS на примерах. В своей наиболее общей форме комбинационная логическая схема или логический элемент, выполняющий булеву функцию, может быть представлена как система с несколькими входами и одним выходом, как показано на рисунке.

Напряжения узлов, связанные с потенциалом земли, представляют все входные переменные. При использовании соглашения о положительной логике булево (или логическое) значение «1» может быть представлено высоким напряжением VDD, а булево (или логическое) значение «0» может быть представлено низким напряжением 0. Выход Узел нагружен емкостью C L , которая представляет собой совокупные емкости паразитного устройства в цепи.

CMOS логические схемы

CMOS Два входа NOR Gate

Схема состоит из параллельно соединенной n-сети и последовательно соединенной дополнительной сети. Входные напряжения V X и V Y подаются на затворы одного nMOS и одного pMOS-транзистора.

Когда один или оба входа высоки, т.е. когда n-сеть создает проводящий путь между выходным узлом и землей, p-сеть обрезается. Если оба входных напряжения низки, т.е. n-сеть отключена, то p-сеть создает проводящий путь между выходным узлом и напряжением питания.

Для любой данной комбинации входов структура дополнительной цепи такова, что выход подключен либо к V DD, либо к земле через тракт с низким сопротивлением, а путь постоянного тока между V DD и землей не установлен для любых комбинаций входов. Выходное напряжение CMOS, два входных затвора NOR получат низкое логическое напряжение V OL = 0 и высокое логическое напряжение V OH = V DD . Уравнение порогового напряжения переключения V th дается выражением

Vth left(NOR2 right)= fracVT,n+ frac12 sqrt frackpkn left(VDD− left|VT,p right| right)1+ frac12 sqrt frackpkn

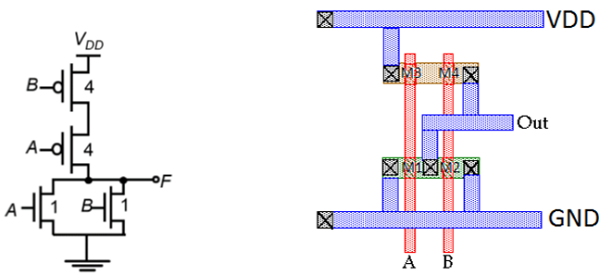

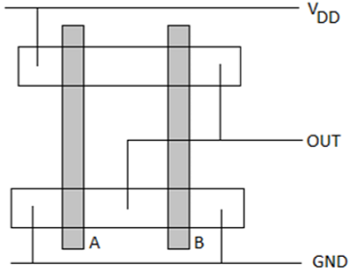

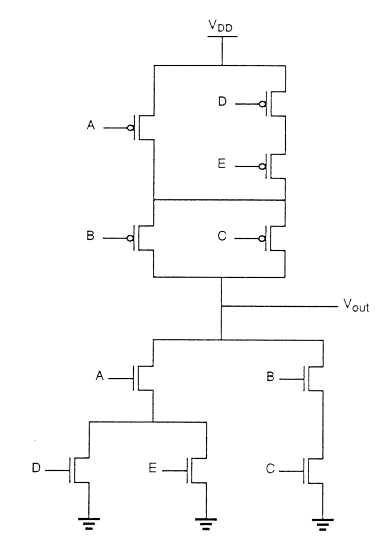

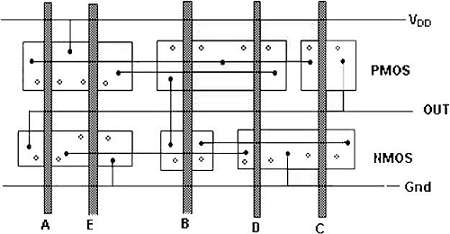

Компоновка CMOS 2-входной NOR Gate

На рисунке показан пример компоновки затвора CMOR с 2 входами NOR с использованием однослойного металла и однослойного поликремния. Особенности этого макета —

- Отдельные вертикальные полилинии для каждого входа

- Отдельные активные формы для N и P устройств соответственно

- Металлические автобусы ходовые горизонтальные

Диаграмма привязки для затвора CMOS N0R2 показана на рисунке ниже; который напрямую соответствует макету, но не содержит информации W и L. Области диффузии изображены прямоугольниками, металлические соединения и сплошные линии и круги, соответственно, представляют контакты, а заштрихованные полосы представляют столбцы поликремния. Стик-диаграмма полезна для планирования оптимальной топологии топологии.

CMOS с двумя входами NAND Gate

Принципиальная схема двух входных затворов CMOS NAND приведена на рисунке ниже.

Принцип работы схемы является двойным по сравнению с КМОП с двумя входами или без операции. N-сеть, состоящая из двух последовательно соединенных nMOS-транзисторов, создает проводящий путь между выходным узлом и землей, если оба входных напряжения имеют высокий логический уровень. Оба параллельно подключенных pMOS-транзистора в p-net будут отключены.

Для всех остальных комбинаций входов, один или оба транзистора pMOS будут включены, а сеть p-net отключена, создавая тем самым путь тока между выходным узлом и напряжением источника питания. Порог переключения для этого затвора получается как —

V_ {th} \ left (NAND2 \ right) = \ frac {V_ {T, n} +2 \ sqrt {\ frac {k_ {p}} {k_ {n}} \ left (V_ {DD} — \ left | V_ {T, p} \ right | \ right)}} {1 + 2 \ sqrt {\ frac {k_ {p}} {k_ {n}}}}

Особенности этого макета следующие —

- Одиночные линии поликремния для входов проходят вертикально по активным областям N и P.

- Отдельные активные фигуры используются для построения как устройств nMOS, так и обоих устройств pMOS.

- Шина питания проходит горизонтально через верх и низ макета.

- Выходные провода проходят горизонтально для легкого подключения к соседней цепи.

Сложные логические схемы

Комплексный логический элемент с нагрузкой истощения NMOS

Для реализации сложных функций нескольких входных переменных базовые структурные схемы и принципы проектирования, разработанные для NOR и NAND, можно распространить на сложные логические элементы. Возможность реализации сложных логических функций с использованием небольшого количества транзисторов является одной из наиболее привлекательных особенностей логических схем nMOS и CMOS. Рассмотрим в качестве примера следующую булеву функцию.

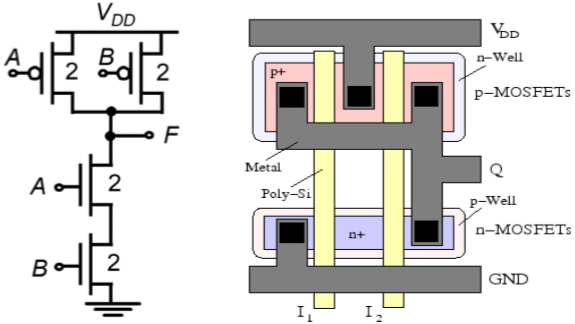

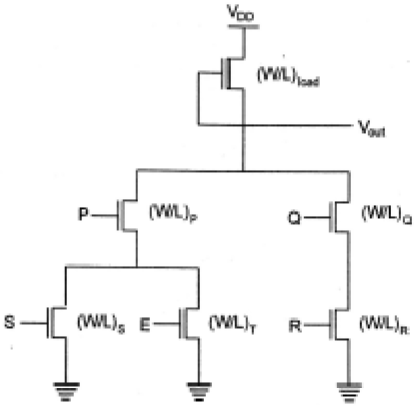

\ overline {Z = P \ left (S + T \ right) + QR}

Комплексный логический элемент с понижающей нагрузкой nMOS, используемый для реализации этой функции, показан на рисунке. На этом рисунке левая ветвь драйвера nMOS из трех транзисторов драйвера используется для выполнения логической функции P (S + T), а правая ветвь выполняет функцию QR. Соединяя две ветви параллельно и помещая нагрузочный транзистор между выходным узлом и напряжением питания V DD , мы получаем заданную комплексную функцию. Каждая входная переменная назначается только одному драйверу.

Проверка топологии схемы дает простые принципы проектирования нисходящей сети —

- Операции ИЛИ выполняются драйверами, подключенными параллельно.

- Операции AND выполняются драйверами, подключенными последовательно.

- Инверсия обеспечивается характером работы схемы MOS.

Если в цепи, реализующей функцию, все входные переменные имеют высокий логический уровень, отношение эквивалентных драйверов (W / L) в нисходящей сети, состоящей из пяти транзисторов nMOS, равно

\ frac {W} {L} = \ frac {1} {\ frac {1} {\ left (W / L \ right) Q} + \ frac {1} {\ left (W / L \ right) R}} + \ frac {1} {\ frac {1} {\ left (W / L \ right) P} + \ frac {1} {\ left (W / L \ right) S + \ left (W / L \ right) Q}}

Комплекс CMOS Logic Gates

Реализация n-сети, или нисходящей сети, основана на тех же базовых принципах проектирования, которые использовались для комплексной логической схемы с понижающей нагрузкой nMOS. Подтверждающая сеть pMOS должна быть двойной сетью сети n-net.

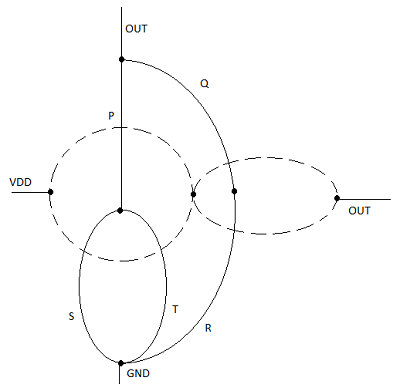

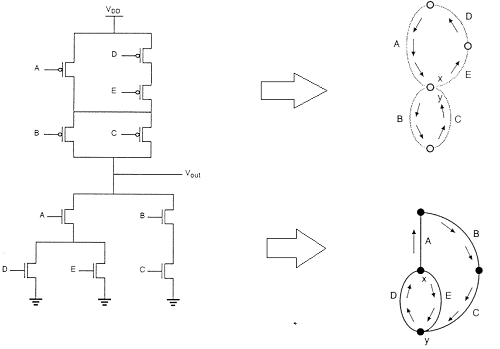

Это означает, что все параллельные соединения в сети nMOS будут соответствовать последовательному соединению в сети pMOS, а все последовательные соединения в сети nMOS соответствуют параллельному соединению в сети pMOS. На рисунке показана простая конструкция двойного графа p-net (подтягивающий) из графа n-net (нисходящий).

Каждый управляющий транзистор в ниспадающей сети обозначен символом ai, а каждый узел — вершиной на ниспадающем графике. Затем новая вершина создается внутри каждой ограниченной области в графе вытягивания, и соседние вершины соединяются ребрами, которые пересекают каждое ребро в графе раскрытия только один раз. Этот новый график показывает подтягивающую сеть.

Техника размещения с использованием метода графа Эйлера

На рисунке показана реализация CMOS сложной функции и ее схема с произвольным упорядочением шлюза, что дает очень неоптимальную компоновку для шлюза CMOS.

В этом случае разделение между столбцами поликремния должно обеспечивать разделение между диффузией и диффузией. Это, безусловно, потребляет значительное количество дополнительной площади кремния.

Используя путь Эйлера, мы можем получить оптимальное расположение. Путь Эйлера определяется как непрерывный путь, который пересекает каждое ребро (ветвь) графа ровно один раз. Найдите путь Эйлера как в графе ниспадающего дерева, так и в графе ниспадающего дерева с одинаковым порядком входов.

VLSI Design — последовательные логические схемы MOS

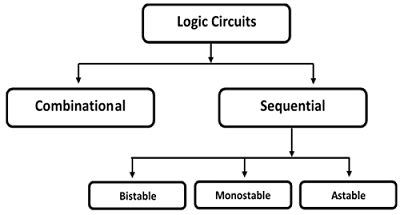

Логические схемы делятся на две категории — (а) комбинированные цепи и (б) последовательные цепи.

В комбинационных цепях выход зависит только от состояния последних входов.

В последовательных цепях выход зависит не только от последних входов, но и от состояния более ранних входов. Последовательные схемы содержат элементы памяти.

Последовательные цепи бывают трех типов:

Бистабильный — Бистабильные схемы имеют две устойчивые рабочие точки и будут в любом из состояний. Пример — ячейки памяти, защелки, триггеры и регистры.

Моностабильные. Моностабильные схемы имеют только одну стабильную рабочую точку, и даже если они временно возмущены до противоположного состояния, они вовремя вернутся к своей стабильной рабочей точке. Пример: таймеры, генераторы импульсов.

Нестабильный — схемы не имеют стабильной рабочей точки и колеблются между несколькими состояниями. Пример — Кольцевой генератор.

CMOS логические схемы

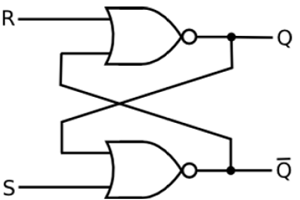

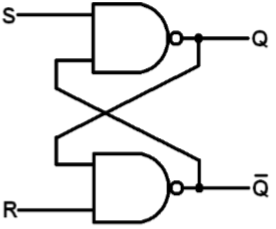

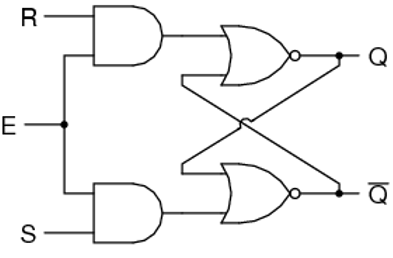

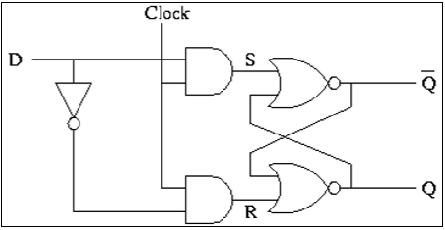

SR Latch на основе NOR Gate

Если установленный вход (S) равен логике «1», а вход сброса равен логике «0». тогда на выходе Q будет установлен логический «1» . В то время как \ overline {Q} принуждается к логике «0» . Это означает, что фиксатор SR будет установлен независимо от его предыдущего состояния.

Точно так же, если S равно «0», а R равно «1», выход Q будет принудительно установлен в «0», а \ overline {Q} — «1» . Это означает, что защелка сбрасывается независимо от ее ранее удержанного состояния. Наконец, если оба входа S и R равны логике «1», тогда оба выхода будут вынуждены к логике «0», что противоречит комплементарности Q и \ overline {Q} .

Следовательно, эта входная комбинация не допускается при нормальной работе. Таблица истинности SR Latch на основе NOR приведена в табл.

| S | р | Q | \ Overline {Q} | операция |

|---|---|---|---|---|

| 0 | 0 | Q | \ Overline {Q} | Держать |

| 1 | 0 | 1 | 0 | Задавать |

| 0 | 1 | 0 | 1 | Сброс |

| 1 | 1 | 0 | 0 | Не положено |

Защелка CMOS SR на основе затвора NOR показана на рисунке ниже.

Если S равно V OH, а R равно V OL , оба параллельно подключенных транзистора M1 и M2 будут включены. Напряжение на узле \ overline {Q} примет логически низкий уровень V OL = 0.

В то же время оба M3 и M4 выключаются, что приводит к появлению высокого логического напряжения V OH в узле Q. Если R равно V OH, а S равно V OL , M1 и M2 выключаются и M3 и M4 включены.

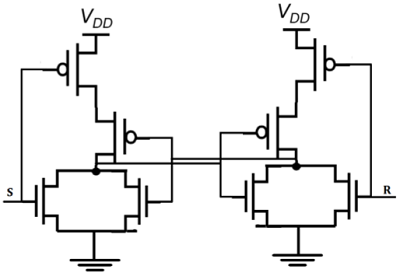

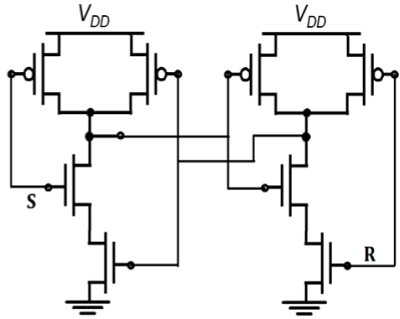

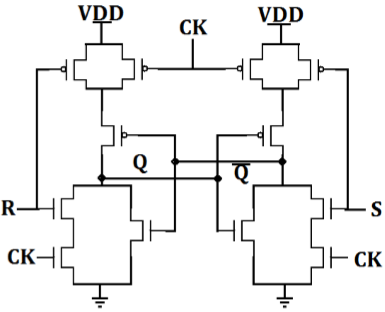

SR Latch на основе NAND Gate

Блок-схема и схема уровня затвора SR-защелки на основе NAND показаны на рисунке. Маленькие кружки на входных клеммах S и R означают, что схема реагирует на активные входные сигналы низкого уровня. Таблица истинности защелки SR на основе NAND приведена в таблице.

| S | р | Q | Q ‘ | |

| 0 | 0 | Северная Каролина | Северная Каролина | Без изменений. Защелка осталась в нынешнем состоянии. |

| 1 | 0 | 1 | 0 | Защелка SET. |

| 0 | 1 | 0 | 1 | Защелка СБРОС. |

| 1 | 1 | 0 | 0 | Неверное состояние. |

Если S переходит в 0 (в то время как R = 1), Q поднимается высоко, вытягивая \ overline {Q} низко, и защелка переходит в состояние Set

S = 0, тогда Q = 1 (если R = 1 )

Если R становится равным 0 (в то время как S = 1), Q поднимается высоко, вытягивая \ overline {Q} низко, и фиксатор сбрасывается

R = 0, тогда Q = 1 (если S = 1 )

Удержание требует, чтобы и S, и R были высокими. Если S = R = 0, то вывод не разрешен, так как это приведет к неопределенному состоянию. CMOS SR Latch на базе NAND Gate показан на рисунке.

Истощение нагрузки nMOS SR Latch на основе NAND Gate показано на рисунке. Операция аналогична защелке CMOS NAND SR. Реализация схемы CMOS имеет низкое рассеивание статической мощности и высокий запас по шуму.

CMOS логические схемы

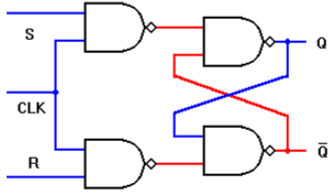

Clocked SR Latch

На рисунке показана защелка SR на основе NOR с добавленными часами. Защелка реагирует на входы S и R только при высоком уровне CLK.

Когда CLK низкий, защелка сохраняет свое текущее состояние. Обратите внимание, что Q меняет состояние —

- Когда S повышается во время положительного CLK.

- На переднем крае CLK после изменений в S & R в течение низкого времени CLK.

- Положительный сбой в S, пока CLK высокий

- Когда R повышается во время положительного CLK.

Реализация CMO AOI тактового SR-защелки на основе NOR показана на рисунке. Обратите внимание, что требуется только 12 транзисторов.

-

Когда CLK низкий, два последовательных терминала в N-дереве N открыты, и два параллельных транзистора в дереве P включены, таким образом сохраняя состояние в ячейке памяти.

-

Когда часы высокие, схема становится просто защелкой CMOS на основе NOR, которая будет реагировать на входы S и R.

Когда CLK низкий, два последовательных терминала в N-дереве N открыты, и два параллельных транзистора в дереве P включены, таким образом сохраняя состояние в ячейке памяти.

Когда часы высокие, схема становится просто защелкой CMOS на основе NOR, которая будет реагировать на входы S и R.

Clocked SR Latch на основе NAND Gate

Схема реализована с четырьмя вентилями NAND. Если эта схема реализована с CMOS, то для нее требуется 16 транзисторов.

- Защелка реагирует на S или R, только если CLK высокий.

- Если и входные сигналы, и сигналы CLK имеют высокий активный уровень: то есть выход Q защелки будет установлен, когда CLK = «1» S = «1» и R = «0»

- Аналогично, защелка будет сброшена, когда CLK = «1,» S = «0» и

Когда CLK низкий, защелка сохраняет свое текущее состояние.

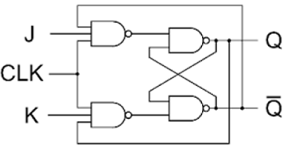

Замкнутый JK Latch

На рисунке выше показана защелка JK с синхронизацией, основанная на вентилях NAND. Недостаток SR-защелки состоит в том, что, когда S и R высоки, его выходное состояние становится неопределенным. Защелка JK устраняет эту проблему, используя обратную связь от вывода к вводу, так что все входные состояния таблицы истинности допустимы. Если J = K = 0, защелка сохранит свое текущее состояние.

Если J = 1 и K = 0, фиксатор будет установлен на следующем положительном фронте тактового сигнала, т.е. Q = 1, \ overline {Q} = 0

Если J = 0 и K = 1, фиксатор будет сброшен на следующем положительном фронте тактового сигнала, то есть Q = 1 и \ overline {Q} = 0.

Если J = K = 1, защелка переключится на следующем положительном фронте часов

Работа синхронизированной защелки JK суммирована в таблице истинности, приведенной в таблице.

|

J |

К |

Q |

\ Overline {Q} |

S |

р |

Q |

\ Overline {Q} |

операция |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Держать |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Сброс |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Задавать |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | тумблер |

| 1 | 0 | 1 | 0 | 0 | 1 |

J

К

Q

S

р

Q

операция

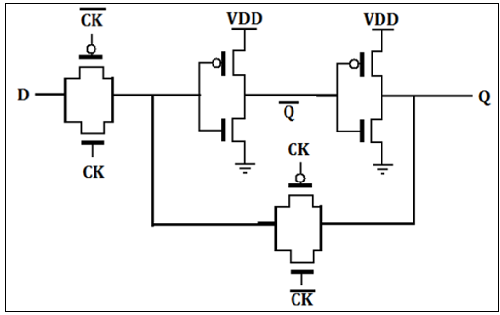

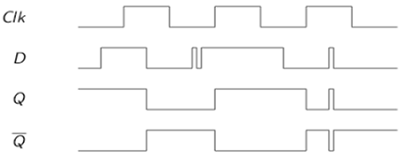

Внедрение CMOS D Latch

Защелка D обычно реализуется с помощью переключателей затвора передачи (TG), как показано на рисунке. Вход TG активируется с помощью CLK, а петля обратной связи с защелкой TG активируется с помощью CLK. Вход D принимается, когда CLK высокий. Когда CLK становится низким, входная цепь разомкнута, и защелка устанавливается с предыдущими данными D.

VLSI Design — VHDL Введение

VHDL расшифровывается как язык описания аппаратного обеспечения для высокоскоростных интегральных схем. Это язык программирования, используемый для моделирования цифровой системы с помощью потока данных, поведенческого и структурного стиля моделирования. Этот язык был впервые введен в 1981 году для Министерства обороны США в рамках программы VHSIC.

Описание дизайна

В VHDL сущность используется для описания аппаратного модуля. Сущность может быть описана с использованием,

- Декларация объекта

- Архитектура

- конфигурация

- Декларация пакета

- Корпус

Посмотрим что это?

Декларация организации

Он определяет имена, входные выходные сигналы и режимы аппаратного модуля.

Синтаксис —

entity entity_name is Port declaration; end entity_name;

Объявление сущности должно начинаться с «сущности» и заканчиваться ключевыми словами «конец». Направление будет входным, выходным или входным.

| В | Порт можно прочитать |

| Из | Порт может быть написан |

| Inout | Порт можно читать и писать |

| буфер | Порт можно читать и писать, он может иметь только один источник. |

Архитектура —

Архитектура может быть описана с использованием структурного, потока данных, поведенческого или смешанного стиля.

Синтаксис —

architecture architecture_name of entity_name architecture_declarative_part; begin Statements; end architecture_name;

Здесь мы должны указать имя объекта, для которого мы пишем тело архитектуры. Операторы архитектуры должны находиться внутри ключевых слов begin и end. Декларативная часть архитектуры может содержать переменные, константы или объявление компонента.

Моделирование потока данных

В этом стиле моделирования поток данных через объект выражается с использованием параллельного (параллельного) сигнала. Одновременными утверждениями в VHDL являются WHEN и GENERATE.

Помимо них, назначения, использующие только операторы (AND, NOT, +, *, sll и т. Д.), Также могут использоваться для построения кода.

Наконец, специальный тип назначения, называемый BLOCK, также может быть использован в этом типе кода.

В параллельном коде может использоваться следующее:

- операторы

- Оператор WHEN (WHEN / ELSE или WITH / SELECT / WHEN);

- Утверждение GENERATE;

- БЛОК заявления

Поведенческое моделирование

В этом стиле моделирования поведение объекта как набора операторов выполняется последовательно в указанном порядке. Только операторы, помещенные в PROCESS, FUNCTION или PROCEDURE, являются последовательными.

ПРОЦЕССЫ, ФУНКЦИИ и ПРОЦЕДУРЫ — единственные разделы кода, которые выполняются последовательно.

Однако в целом любой из этих блоков по-прежнему совпадает с любыми другими операторами, размещенными вне его.

Одним из важных аспектов кода поведения является то, что он не ограничен последовательной логикой. Действительно, с его помощью мы можем строить последовательные схемы, а также комбинационные схемы.

Заявления о поведении: IF, WAIT, CASE и LOOP. ПЕРЕМЕННЫЕ также ограничены, и они должны использоваться только в последовательном коде. VARIABLE никогда не может быть глобальным, поэтому его значение не может быть передано напрямую.

Структурное моделирование

В этом моделировании объект описывается как набор взаимосвязанных компонентов. Оператор создания экземпляра компонента является параллельным оператором. Поэтому порядок этих утверждений не важен. Структурный стиль моделирования описывает только взаимосвязь компонентов (рассматриваемых как черные ящики), не подразумевая какого-либо поведения самих компонентов или сущности, которую они коллективно представляют.

В структурном моделировании тело архитектуры состоит из двух частей — декларативной части (до начала ключевого слова) и части инструкции (после начала ключевого слова).

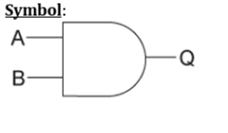

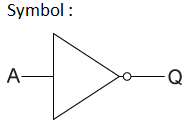

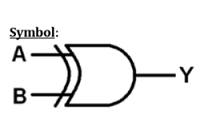

Логическая операция — И ВОРОТА

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity and1 is port(x,y:in bit ; z:out bit); end and1; architecture virat of and1 is begin z<=x and y; end virat;

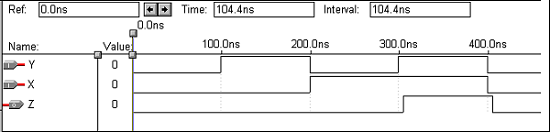

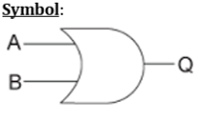

Волновые

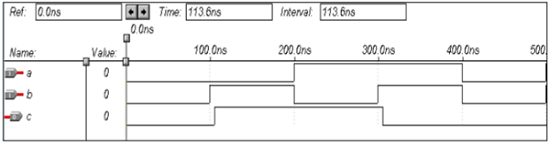

Логическая операция — ИЛИ Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity or1 is port(x,y:in bit ; z:out bit); end or1; architecture virat of or1 is begin z<=x or y; end virat;

Волновые

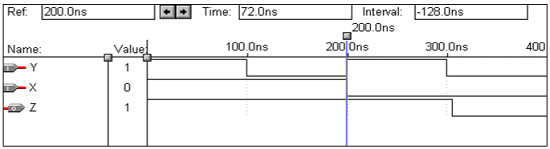

Логическая операция — НЕ Ворота

| Икс | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity not1 is port(x:in bit ; y:out bit); end not1; architecture virat of not1 is begin y<=not x; end virat;

Волновые

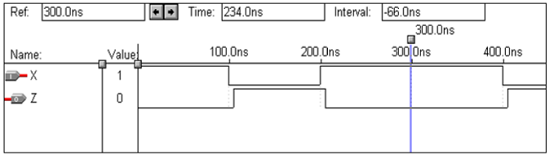

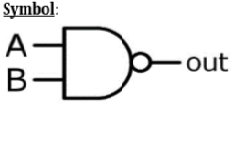

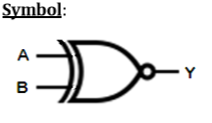

Логическая операция — NAND Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nand1 is port(a,b:in bit ; c:out bit); end nand1; architecture virat of nand1 is begin c<=a nand b; end virat;

Волновые

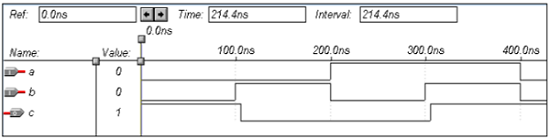

Логическая операция — NOR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity nor1 is port(a,b:in bit ; c:out bit); end nor1; architecture virat of nor1 is begin c<=a nor b; end virat;

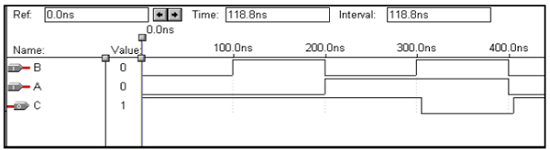

Волновые

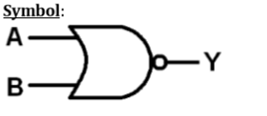

Логическая операция — XOR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xor1 is port(a,b:in bit ; c:out bit); end xor1; architecture virat of xor1 is begin c<=a xor b; end virat;

Волновые

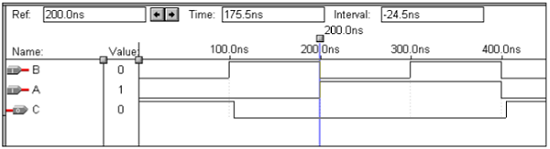

Логическая операция — X-NOR Gate

| Икс | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity xnor1 is port(a,b:in bit ; c:out bit); end xnor1; architecture virat of xnor1 is begin c<=not(a xor b); end virat;

Волновые

VHDL Программирование комбинационных схем

В этой главе описывается программирование VHDL для комбинационных цепей.

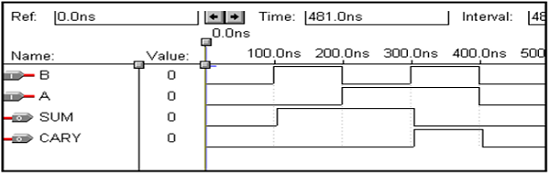

VHDL-код для половины сумматора

VHDL Code: Library ieee; use ieee.std_logic_1164.all; entity half_adder is port(a,b:in bit; sum,carry:out bit); end half_adder; architecture data of half_adder is begin sum<= a xor b; carry <= a and b; end data;

Волновые

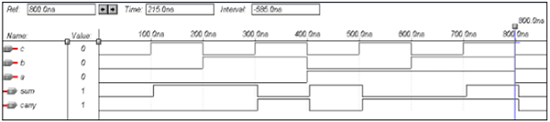

VHDL код для полного сумматора

Library ieee; use ieee.std_logic_1164.all; entity full_adder is port(a,b,c:in bit; sum,carry:out bit); end full_adder; architecture data of full_adder is begin sum<= a xor b xor c; carry <= ((a and b) or (b and c) or (a and c)); end data;

Волновые

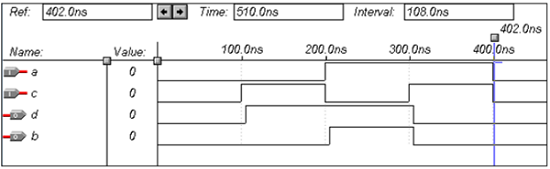

Код VHDL для половины вычитающего

Library ieee; use ieee.std_logic_1164.all; entity half_sub is port(a,c:in bit; d,b:out bit); end half_sub; architecture data of half_sub is begin d<= a xor c; b<= (a and (not c)); end data;

Волновые

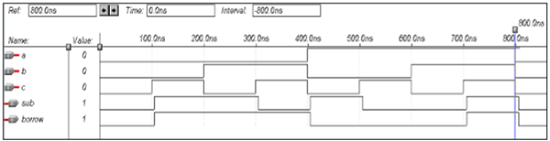

Код VHDL для полного вычитателя

Library ieee; use ieee.std_logic_1164.all; entity full_sub is port(a,b,c:in bit; sub,borrow:out bit); end full_sub; architecture data of full_sub is begin sub<= a xor b xor c; borrow <= ((b xor c) and (not a)) or (b and c); end data;

Волновые

VHDL код для мультиплексора

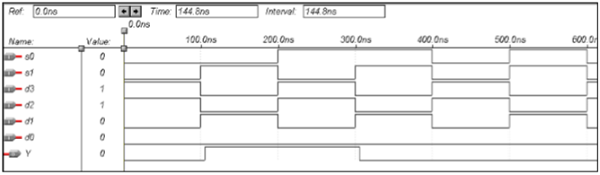

Library ieee; use ieee.std_logic_1164.all; entity mux is port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit); end mux; architecture data of mux is begin Y<= (not S0 and not S1 and D0) or (S0 and not S1 and D1) or (not S0 and S1 and D2) or (S0 and S1 and D3); end data;

Волновые

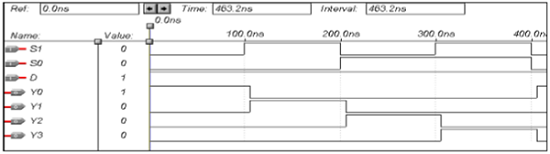

VHDL код для демультиплексора

Library ieee; use ieee.std_logic_1164.all; entity demux is port(S1,S0,D:in bit; Y0,Y1,Y2,Y3:out bit); end demux; architecture data of demux is begin Y0<= ((Not S0) and (Not S1) and D); Y1<= ((Not S0) and S1 and D); Y2<= (S0 and (Not S1) and D); Y3<= (S0 and S1 and D); end data;

Волновые

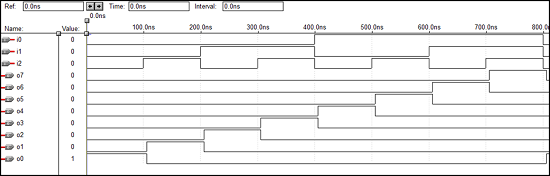

Код VHDL для кодера 8 x 3

library ieee; use ieee.std_logic_1164.all; entity enc is port(i0,i1,i2,i3,i4,i5,i6,i7:in bit; o0,o1,o2: out bit); end enc; architecture vcgandhi of enc is begin o0<=i4 or i5 or i6 or i7; o1<=i2 or i3 or i6 or i7; o2<=i1 or i3 or i5 or i7; end vcgandhi;

Волновые

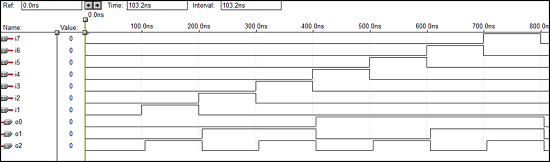

Код VHDL для декодера 3 x 8

library ieee; use ieee.std_logic_1164.all; entity dec is port(i0,i1,i2:in bit; o0,o1,o2,o3,o4,o5,o6,o7: out bit); end dec; architecture vcgandhi of dec is begin o0<=(not i0) and (not i1) and (not i2); o1<=(not i0) and (not i1) and i2; o2<=(not i0) and i1 and (not i2); o3<=(not i0) and i1 and i2; o4<=i0 and (not i1) and (not i2); o5<=i0 and (not i1) and i2; o6<=i0 and i1 and (not i2); o7<=i0 and i1 and i2; end vcgandhi;

Волновые

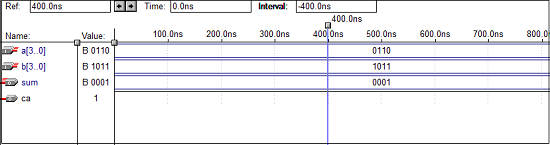

Код VHDL — 4-битный параллельный сумматор

library IEEE; use IEEE.STD_LOGIC_1164.all; entity pa is port(a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); ca : out STD_LOGIC; sum : out STD_LOGIC_VECTOR(3 downto 0) ); end pa; architecture vcgandhi of pa is Component fa is port (a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; sum : out STD_LOGIC; ca : out STD_LOGIC ); end component; signal s : std_logic_vector (2 downto 0); signal temp: std_logic; begin temp<='0'; u0 : fa port map (a(0),b(0),temp,sum(0),s(0)); u1 : fa port map (a(1),b(1),s(0),sum(1),s(1)); u2 : fa port map (a(2),b(2),s(1),sum(2),s(2)); ue : fa port map (a(3),b(3),s(2),sum(3),ca); end vcgandhi;

Волновые

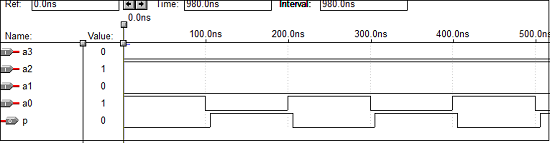

Код VHDL — 4-битный контроль четности

library ieee; use ieee.std_logic_1164.all; entity parity_checker is port (a0,a1,a2,a3 : in std_logic; p : out std_logic); end parity_checker; architecture vcgandhi of parity_checker is begin p <= (((a0 xor a1) xor a2) xor a3); end vcgandhi;

Волновые

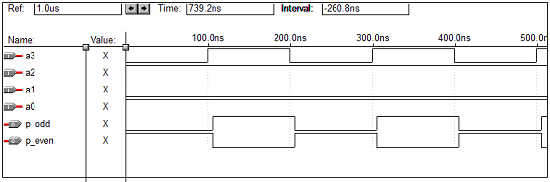

Код VHDL — 4-битный генератор четности

library ieee; use ieee.std_logic_1164.all; entity paritygen is port (a0, a1, a2, a3: in std_logic; p_odd, p_even: out std_logic); end paritygen; architecture vcgandhi of paritygen is begin process (a0, a1, a2, a3) if (a0 ='0' and a1 ='0' and a2 ='0' and a3 =’0’) then odd_out <= "0"; even_out <= "0"; else p_odd <= (((a0 xor a1) xor a2) xor a3); p_even <= not(((a0 xor a1) xor a2) xor a3); end vcgandhi

Волновые

Программирование VHDL для последовательных цепей

В этой главе объясняется, как выполнять программирование VHDL для последовательных цепей.

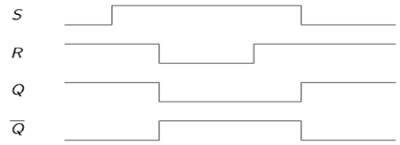

Код VHDL для защелки SR

library ieee; use ieee.std_logic_1164.all; entity srl is port(r,s:in bit; q,qbar:buffer bit); end srl; architecture virat of srl is signal s1,r1:bit; begin q<= s nand qbar; qbar<= r nand q; end virat;

Волновые

Код VHDL для защелки D

library ieee; use ieee.std_logic_1164.all; entity Dl is port(d:in bit; q,qbar:buffer bit); end Dl; architecture virat of Dl is signal s1,r1:bit; begin q<= d nand qbar; qbar<= d nand q; end virat;

Волновые

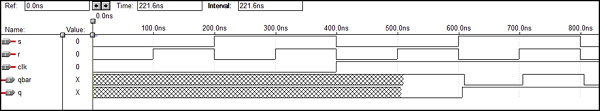

Код VHDL для флип-флопа SR

library ieee; use ieee.std_logic_1164.all; entity srflip is port(r,s,clk:in bit; q,qbar:buffer bit); end srflip; architecture virat of srflip is signal s1,r1:bit; begin s1<=s nand clk; r1<=r nand clk; q<= s1 nand qbar; qbar<= r1 nand q; end virat;

Волновые

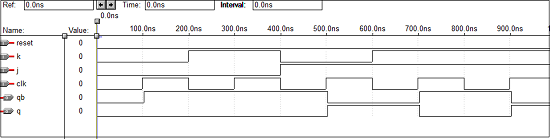

VHDL-код для флип-флопа JK

library IEEE; use IEEE.STD_LOGIC_1164.all; entity jk is port( j : in STD_LOGIC; k : in STD_LOGIC; clk : in STD_LOGIC; reset : in STD_LOGIC; q : out STD_LOGIC; qb : out STD_LOGIC ); end jk; architecture virat of jk is begin jkff : process (j,k,clk,reset) is variable m : std_logic := '0'; begin if (reset = '1') then m : = '0'; elsif (rising_edge (clk)) then if (j/ = k) then m : = j; elsif (j = '1' and k = '1') then m : = not m; end if; end if; q <= m; qb <= not m; end process jkff; end virat;

Волновые

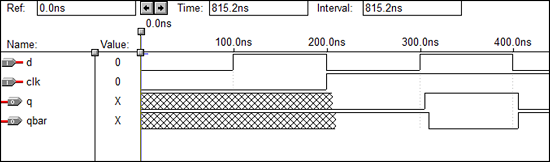

VHDL-код для флип-флопа D

Library ieee; use ieee.std_logic_1164.all; entity dflip is port(d,clk:in bit; q,qbar:buffer bit); end dflip; architecture virat of dflip is signal d1,d2:bit; begin d1<=d nand clk; d2<=(not d) nand clk; q<= d1 nand qbar; qbar<= d2 nand q; end virat;

Волновые

Код VHDL для Т-флип-флоп

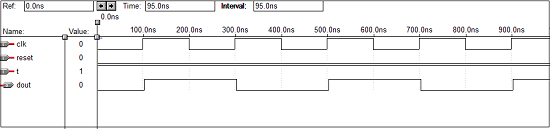

library IEEE; use IEEE.STD_LOGIC_1164.all; entity Toggle_flip_flop is port( t : in STD_LOGIC; clk : in STD_LOGIC; reset : in STD_LOGIC; dout : out STD_LOGIC ); end Toggle_flip_flop; architecture virat of Toggle_flip_flop is begin tff : process (t,clk,reset) is variable m : std_logic : = '0'; begin if (reset = '1') then m : = '0'; elsif (rising_edge (clk)) then if (t = '1') then m : = not m; end if; end if; dout < = m; end process tff; end virat;

Волновые

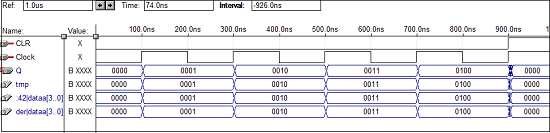

Код VHDL для 4-битного счетчика

library IEEE; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity counter is port(Clock, CLR : in std_logic; Q : out std_logic_vector(3 downto 0) ); end counter; architecture virat of counter is signal tmp: std_logic_vector(3 downto 0); begin process (Clock, CLR) begin if (CLR = '1') then tmp < = "0000"; elsif (Clock'event and Clock = '1') then mp <= tmp + 1; end if; end process; Q <= tmp; end virat;

Волновые

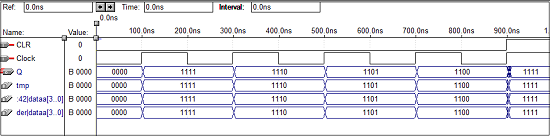

Код VHDL для 4-битного счетчика вниз

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity dcounter is port(Clock, CLR : in std_logic; Q : out std_logic_vector(3 downto 0)); end dcounter; architecture virat of dcounter is signal tmp: std_logic_vector(3 downto 0); begin process (Clock, CLR) begin if (CLR = '1') then tmp <= "1111"; elsif (Clock'event and Clock = '1') then tmp <= tmp - 1; end if; end process; Q <= tmp; end virat;

Волновые

VLSI Design — Verilog Введение

Verilog — ЯЗЫК ОБОРУДОВАНИЯ ДЛЯ ОБОРУДОВАНИЯ (HDL). Это язык, используемый для описания цифровой системы, такой как сетевой коммутатор, микропроцессор, память или триггер. Это означает, что с помощью HDL мы можем описать любое цифровое оборудование на любом уровне. Проекты, которые описаны в HDL, не зависят от технологии, очень просты для проектирования и отладки и, как правило, более полезны, чем схемы, особенно для больших цепей.

Verilog поддерживает дизайн на многих уровнях абстракции. Основные три —

- Поведенческий уровень

- Уровень регистрации-передачи

- Уровень ворот

Поведенческий уровень

Этот уровень описывает систему с помощью параллельных алгоритмов (Поведенческий). Каждый алгоритм является последовательным, что означает, что он состоит из набора инструкций, которые выполняются одна за другой. Функции, задачи и блоки являются основными элементами. Нет никакого отношения к структурной реализации проекта.

Уровень регистрации-передачи

Проекты, использующие Уровень Передачи Регистров, определяют характеристики схемы с использованием операций и передачи данных между регистрами. Современное определение кода RTL — «Любой код, который можно синтезировать, называется кодом RTL».

Уровень ворот

На логическом уровне характеристики системы описываются логическими связями и их временными свойствами. Все сигналы являются дискретными сигналами. Они могут иметь только определенные логические значения (`0 ‘,` 1’, `X ‘,` Z`). Используемые операции — это предопределенные логические примитивы (базовые элементы). Моделирование на уровне ворот может быть неправильной идеей для логического проектирования. Код уровня шлюза генерируется с использованием таких инструментов, как инструменты синтеза, а его список соединений используется для моделирования уровня шлюза и для внутреннего интерфейса.

Лексические жетоны

Исходные текстовые файлы на языке Verilog представляют собой поток лексических токенов. Токен состоит из одного или нескольких символов, и каждый отдельный символ находится ровно в одном токене.

Основные лексические токены, используемые Verilog HDL, аналогичны токенам языка Си. Verilog чувствителен к регистру. Все ключевые слова в нижнем регистре.

Пустое пространство

Пробелы могут содержать символы для пробелов, табуляции, новых строк и каналов. Эти символы игнорируются, кроме случаев, когда они служат для разделения токенов.

Символами пробела являются Пробел, Вкладки, Возврат каретки, Новая строка и Форм подачи.

Комментарии

Есть две формы для представления комментариев

- 1) Однострочные комментарии начинаются с токена // и заканчиваются возвратом каретки.

Пример: // это однострочный синтаксис

- 2) Многострочные комментарии начинаются с токена / * и заканчиваются токеном * /

Пример: / * это многострочный синтаксис * /

чисел

Вы можете указать число в двоичном, восьмеричном, десятичном или шестнадцатеричном формате. Отрицательные числа представлены в 2 комплимент номера. Verilog позволяет целые числа, действительные числа и числа со знаком и без знака.

Синтаксис задается как — <size> <radix> <value>

Размер или число без размера может быть определено в <Size>, а <radix> определяет, является ли оно двоичным, восьмеричным, шестнадцатеричным или десятичным.

Идентификаторы

Идентификатор — это имя, используемое для определения объекта, такого как функция, модуль или регистр. Идентификаторы должны начинаться с буквенных символов или символов подчеркивания. Ex. A_Z, a_z, _

Идентификаторы представляют собой комбинацию букв, цифр, символов подчеркивания и $. Они могут быть длиной до 1024 символов.

операторы

Операторы — это специальные символы, используемые для обозначения условий или для работы с переменными. Для выполнения операций с переменными используются один, два, а иногда и три символа.

Ex. >, +, ~, &! знак равно

Verilog Ключевые слова

Слова, имеющие особое значение в Verilog, называются ключевыми словами Verilog. Например, назначьте, case, while, wire, reg, и, или, nand и module. Они не должны использоваться в качестве идентификаторов. Ключевые слова Verilog также включают в себя директивы компилятора, а также системные задачи и функции.

Моделирование уровня ворот

В Verilog есть встроенные примитивы, такие как логические вентили, вентили передачи и переключатели. Они редко используются для проектных работ, но они используются в мире после синтеза для моделирования ячеек ASIC / FPGA.

Моделирование на уровне ворот имеет два свойства:

Сила привода — Сила выходных ворот определяется силой привода. Выход наиболее сильный, если есть прямая связь с источником. Прочность снижается, если соединение осуществляется через проводящий транзистор и, по меньшей мере, при подключении через резистор с повышением / понижением. Сила привода обычно не указывается, в этом случае по умолчанию используются значения strong1 и strong0.

Задержки — если задержки не указаны, то у ворот нет задержек распространения; если указаны две задержки, то первая представляет задержку нарастания, а вторая — задержку нарастания; если указана только одна задержка, то оба, подъем и спад равны. Задержки могут быть проигнорированы при синтезе.

Примитивы ворот

Основные логические элементы используют один выход, а в Verilog используется множество входов. GATE использует одно из ключевых слов — и, nand, или, или, ни, xor, xnor для использования в Verilog для N числа входов и 1 выхода.

Example: Module gate() Wire ot0; Wire ot1; Wire ot2; Reg in0,in1,in2,in3; Not U1(ot0,in0); Xor U2(ot1,in1,in2,in3); And U3(ot2, in2,in3,in0)

Примитивы ворот передачи

Примитивы шлюза передачи включают как буферы, так и инверторы. Они имеют один вход и один или несколько выходов. В синтаксисе создания шлюза, показанном ниже, GATE обозначает либо ключевое слово buf, либо NOT gate.

Пример: Not, buf, bufif0, bufif1, notif0, notif1

Нет — выходной инвертор

Buf — n выходной буфер

Bufifo — трехсторонний буфер, активный низкий уровень разрешения

Bufif1 — трехсторонний буфер, активная активация высокого уровня

Notifo — трехсторонний инвертор, активный низкий уровень разрешения

Notif1 — трехсторонний инвертор, активный высокий уровень разрешения

Example: Module gate() Wire out0; Wire out1; Reg in0,in1; Not U1(out0,in0); Buf U2(out0,in0);

Типы данных

Набор значений

Verilog состоит, в основном, из четырех основных ценностей. Все типы данных Verilog, которые используются в Verilog, хранят эти значения —

0 (логический ноль или ложное условие)

1 (логическая единица или истинное условие)

х (неизвестное логическое значение)

z (состояние высокого сопротивления)

использование x и z очень ограничено для синтеза.

провод

Провод используется для представления физического провода в цепи, и он используется для подключения ворот или модулей. Значение провода может быть прочитано и не назначено в функции или блоке. Провод не может хранить значение, но всегда управляется оператором непрерывного присваивания или подключением провода к выходу вентиля / модуля. Другие конкретные типы проводов —

Wand (wired-AND) — здесь значение Wand зависит от логического AND всех подключенных к нему драйверов устройств.

Wor (wired-OR) — здесь значение Wor зависит от логического ИЛИ всех подключенных к нему драйверов устройств.

Три (три состояния) — здесь все драйверы, подключенные к три, должны быть z, кроме одного (который определяет значение три).

Example: Wire [msb:lsb] wire_variable_list; Wirec // simple wire Wand d; Assign d = a; // value of d is the logical AND of Assign d = b; // a and b Wire [9:0] A; // a cable (vector) of 10 wires. Wand [msb:lsb] wand_variable_list; Wor [msb:lsb] wor_variable_list; Tri [msb:lsb] tri_variable_list;

регистр

Reg (регистр) — это объект данных, который содержит значение от одного процедурного присвоения следующему и используется только в различных функциях и процедурных блоках. Reg — это простой Verilog регистр переменного типа, который не может подразумевать физический регистр. В многобитовых регистрах данные хранятся в виде чисел без знака, а расширение знака не используется.

Пример —

рег с; // одиночная 1-битная регистровая переменная

рег [5: 0] драгоценный камень; // 6-битный вектор;

рег [6: 0] д, е; // две 7-битные переменные

Вход, Выход, Вход

Эти ключевые слова используются для объявления входных, выходных и двунаправленных портов задачи или модуля. Здесь входные и выходные порты имеют проводной тип, а выходной порт настроен на проводной, reg, wand, wor или tri. Всегда по умолчанию используется тип провода.

пример

Module sample(a, c, b, d); Input c; // An input where wire is used. Output a, b; // Two outputs where wire is used. Output [2:0] d; /* A three-bit output. One must declare type in a separate statement. */ reg [1:0] a; // The above ‘a’ port is for declaration in reg.

целое число

Целые числа используются в переменных общего назначения. Они используются в основном в циклах-индикаторах, константах и параметрах. Они имеют тип данных ‘reg’. Они хранят данные как числа со знаком, тогда как явно объявленные типы reg хранят их как данные без знака. Если целое число не определено во время компиляции, тогда размер по умолчанию будет 32 бита.

Если целое число содержит константу, синтезатор настраивает их на минимальную ширину, необходимую во время компиляции.

пример

Integer c; // single 32-bit integer Assign a = 63; // 63 defaults to a 7-bit variable.

Supply0, Supply1

Supply0 определяет провода, связанные с логикой 0 (земля), и supply1 определяют провода, связанные с логикой 1 (питание).

пример

supply0 logic_0_wires; supply0 gnd1; // equivalent to a wire assigned as 0 supply1 logic_1_wires; supply1 c, s;

Время

Время — это 64-разрядная величина, которую можно использовать вместе с системной задачей $ time для хранения времени моделирования. Время не поддерживается для синтеза и, следовательно, используется только для целей моделирования.

пример

time time_variable_list; time c; c = $time; //c = current simulation time

параметр

Параметр определяет константу, которая может быть установлена при использовании модуля, что позволяет настраивать модуль в процессе создания экземпляра.

Example Parameter add = 3’b010, sub = 2’b11; Parameter n = 3; Parameter [2:0] param2 = 3’b110; reg [n-1:0] jam; /* A 3-bit register with length of n or above. */ always @(z) y = {{(add - sub){z}}; if (z) begin state = param2[1]; else state = param2[2]; end

операторы

Арифметические Операторы

Эти операторы выполняют арифметические операции. + И − используются как унарные (x) или бинарные (z − y) операторы.

Операторы, которые включены в арифметическую операцию:

+ (сложение), — (вычитание), * (умножение), / (деление),% (модуль)

Пример —

parameter v = 5; reg[3:0] b, d, h, i, count; h = b + d; i = d - v; cnt = (cnt +1)%16; //Can count 0 thru 15.

Операторы отношений

Эти операторы сравнивают два операнда и возвращают результат в одном бите, 1 или 0.

Переменные проводов и регистров положительные. Таким образом (-3’d001) = = 3’d111 и (-3b001)> 3b110.

Операторы, которые включены в реляционную операцию:

- == (равно)

- != (Не равно)

- > (больше чем)

- > = (больше или равно)

- <(меньше чем)

- <= (меньше или равно)

пример

if (z = = y) c = 1; else c = 0; // Compare in 2’s compliment; d>b reg [3:0] d,b; if (d[3]= = b[3]) d[2:0] > b[2:0]; else b[3]; Equivalent Statement e = (z == y);

Битовые операторы

Побитовые операторы, которые делают побитовое сравнение двух операндов.

Операторы, включенные в побитовую операцию:

- & (побитовое И)

- | (BitwiseOR)

- ~ (поразрядно НЕ)

- ^ (побитовый XOR)

- ~ ^ или ^ ~ (побитовый XNOR)

пример

module and2 (d, b, c); input [1:0] d, b; output [1:0] c; assign c = d & b; end module

Логические Операторы

Логические операторы являются побитовыми операторами и используются только для одноразрядных операндов. Они возвращают одно битовое значение, 0 или 1. Они могут работать с целыми числами или группой битов, выражениями и обрабатывать все ненулевые значения как 1. Логические операторы обычно используются в условных выражениях, так как они работают с выражениями.

Операторы, которые включены в логическую операцию:

- ! (логическое НЕ)

- && (логическое И)

- || (логическое ИЛИ)

пример

wire[7:0] a, b, c; // a, b and c are multibit variables. reg x; if ((a == b) && (c)) x = 1; //x = 1 if a equals b, and c is nonzero. else x = !a; // x =0 if a is anything but zero.

Операторы сокращения

Операторы редукции являются унарной формой битовых операторов и работают со всеми битами вектора-операнда. Они также возвращают однобитное значение.

Операторы, которые включены в операцию сокращения:

- & (сокращение И)

- | (сокращение ИЛИ)

- ~ & (сокращение NAND)

- ~ | (сокращение NOR)

- ^ (сокращение XOR)

- ~ ^ или ^ ~ (сокращение XNOR)

пример

Module chk_zero (x, z); Input [2:0] x; Output z; Assign z = & x; // Reduction AND End module

Операторы смены

Операторы сдвига, которые смещают первый операнд на количество битов, указанное вторым операндом в синтаксисе. Свободные позиции заполнены нулями для обоих направлений, сдвигов влево и вправо (расширение знака использования не используется).

Операторы, которые включены в операцию сдвига:

- << (сдвиг влево)

- >> (сдвиг вправо)

пример

Assign z = c << 3; /* z = c shifted left 3 bits;

Вакансии заполнены нулями * /

Оператор конкатенации

Оператор конкатенации объединяет два или более операнда для формирования большего вектора.

Оператор, включенный в операцию конкатенации, — — {} (конкатенация)

пример

wire [1:0] a, h; wire [2:0] x; wire [3;0] y, Z; assign x = {1’b0, a}; // x[2] = 0, x[1] = a[1], x[0] = a[0] assign b = {a, h}; /* b[3] = a[1], b[2] = a[0], b[1] = h[1], b[0] = h[0] */ assign {cout, b} = x + Z; // Concatenation of a result

Оператор репликации

Оператор репликации делает несколько копий элемента.

Оператор, используемый в операции репликации, — — {n {item}} (n-кратная репликация элемента)

пример

Wire [1:0] a, f; wire [4:0] x; Assign x = {2{1’f0}, a}; // Equivalent to x = {0,0,a } Assign y = {2{a}, 3{f}}; //Equivalent to y = {a,a,f,f} For synthesis, Synopsis did not like a zero replication. For example:- Parameter l = 5, k = 5; Assign x = {(l-k){a}}

Условный оператор

Условный оператор синтезирует в мультиплексор. Это тот же тип, который используется в C / C ++ и оценивает одно из двух выражений на основе условия.

Оператор, используемый в условной операции:

(Состояние) ? (Результат, если условие истинно) —

(результат, если условие ложно)

пример

Assign x = (g) ? a : b; Assign x = (inc = = 2) ? x+1 : x-1; /* if (inc), x = x+1, else x = x-1 */

Операнды

литералы

Литералы — это операнды с постоянными значениями, которые используются в выражениях Verilog. Два часто используемых литерала Verilog —

-

String — Строковый литеральный операнд — это одномерный массив символов, заключенный в двойные кавычки («»).

-

Числовой — операнд с постоянным числом указывается в двоичном, восьмеричном, десятичном или шестнадцатеричном формате.

String — Строковый литеральный операнд — это одномерный массив символов, заключенный в двойные кавычки («»).

Числовой — операнд с постоянным числом указывается в двоичном, восьмеричном, десятичном или шестнадцатеричном формате.

пример

n — целое число, представляющее количество бит

F — один из четырех возможных базовых форматов —

b для двоичного, o для восьмеричного, d для десятичного, h для шестнадцатеричного.

“time is” // string literal 267 // 32-bit decimal number 2’b01 // 2-bit binary 20’hB36F // 20-bit hexadecimal number ‘062 // 32-bit octal number

Провода, регистры и параметры

Провода, регистры и параметры — это типы данных, используемые в качестве операндов в выражениях Verilog.

Выбор битов «x [2]» и выбор партий «x [4: 2]»

Выбор битов и выбор частей используются для выбора одного бита и нескольких битов соответственно из провода, регистра или вектора параметров с использованием квадратных скобок «[]». Выборки битов и выборки частей также используются как выражения в выражениях так же, как используются их основные объекты данных.

пример

reg [7:0] x, y; reg [3:0] z; reg a; a = x[7] & y[7]; // bit-selects z = x[7:4] + y[3:0]; // part-selects

Вызовы функций

В вызовах функций возвращаемое значение функции используется непосредственно в выражении без необходимости сначала назначать его в регистр или провод. Он просто помещает вызов функции в качестве одного из типов операндов. Это необходимо, чтобы убедиться, что вы знаете ширину в битах возвращаемого значения вызова функции.

Example Assign x = y & z & chk_yz(z, y); // chk_yz is a function . . ./* Definition of the function */ Function chk_yz; // function definition Input z,y; chk_yz = y^z; End function

Модули

Декларация модуля

В Verilog, модуль является основным объектом проектирования. Это указывает на имя и список портов (аргументы). Следующие несколько строк, которые определяют тип ввода / вывода (вход, выход или выход) и ширину каждого порта. Ширина порта по умолчанию составляет всего 1 бит. Переменные порта должны быть объявлены wire, wand ,. , ., рег. Переменная порта по умолчанию — проводная. Обычно входы являются проводными, потому что их данные защелкиваются вне модуля. Выходы имеют тип reg, если их сигналы хранятся внутри.

пример

module sub_add(add, in1, in2, out); input add; // defaults to wire input [7:0] in1, in2; wire in1, in2; output [7:0] out; reg out; ... statements ... End module

Непрерывное назначение

Непрерывное назначение в модуле используется для назначения значения проводнику, которое является обычным назначением, используемым снаружи всегда или начальных блоков. Это присваивание выполняется с помощью явного оператора присваивания или для присвоения значения проводу во время его объявления. Непрерывные задания выполняются непрерывно во время симуляции. Порядок присваивания операторов не влияет на это. Если вы сделаете какие-либо изменения в любом из входных сигналов с правой стороны, это изменит выходной сигнал с левой стороны.

пример

Wire [1:0] x = 2’y01; // assigned on declaration Assign y = c | d; // using assign statement Assign d = a & b; /* the order of the assign statements does not matter. */

Модульные реализации

Объявления модулей — это шаблоны для создания реальных объектов. Модули создаются внутри других модулей, и каждое создание создает один объект из этого шаблона. Исключением является модуль верхнего уровня, который является его собственным экземпляром. Порты модуля должны соответствовать тем, которые определены в шаблоне. Указано —

-

По имени , используя точку «.template имя порта (название провода, подключенного к порту)». Или же

-

По положению расположение портов в одном и том же месте в списках портов как шаблона, так и экземпляра.

По имени , используя точку «.template имя порта (название провода, подключенного к порту)». Или же

По положению расположение портов в одном и том же месте в списках портов как шаблона, так и экземпляра.

пример

MODULE DEFINITION Module and4 (x, y, z); Input [3:0] x, y; Output [3:0] z; Assign z = x | y; End module

Поведенческое моделирование и сроки в Verilog

Поведенческие модели в Verilog содержат процедурные операторы, которые управляют симуляцией и манипулируют переменными типов данных. Все эти утверждения содержатся в процедурах. С каждой процедурой связан поток операций.

Во время моделирования поведенческой модели все потоки, определенные операторами «Always» и «Initial», начинаются вместе во время моделирования «ноль». Первоначальные операторы выполняются один раз, а операторы Always выполняются многократно. В этой модели регистровые переменные a и b инициализируются в двоичные 1 и 0 соответственно во время моделирования «ноль». Первоначальный оператор затем завершается и не выполняется снова во время этого прогона моделирования. Этот начальный оператор содержит блок начала-конца (также называемый последовательным блоком) операторов. В этом блоке типа begin-end сначала инициализируется a, а затем b.

Пример поведенческого моделирования

module behave; reg [1:0]a,b; initial begin a = ’b1; b = ’b0; end always begin #50 a = ~a; end always begin #100 b = ~b; end End module

Процедурные Назначения

Процедурные присвоения предназначены для обновления переменных типа reg, integer, time и memory. Существует существенная разница между процедурным назначением и непрерывным назначением, как описано ниже —

Непрерывные назначения управляют сетевыми переменными и оцениваются и обновляются всякий раз, когда входной операнд изменяет значение.

Процедурные присваивания обновляют значение переменных регистра под контролем окружающих их процедур процедурного потока.

Правая часть процедурного присваивания может быть любым выражением, которое оценивает значение. Тем не менее, выбор части справа должен иметь постоянные индексы. Левая сторона указывает переменную, которая получает назначение с правой стороны. Левая часть процессуального назначения может принимать одну из следующих форм —

-

регистровая, целочисленная, вещественная или временная переменная — присвоение ссылки на имя одного из этих типов данных.

-

выбор бита для регистровой, целочисленной, действительной или временной переменной — назначение одного бита, при котором остальные биты остаются нетронутыми.

-

частичный выбор регистра, целочисленная, вещественная или временная переменная — частичный выбор из двух или более смежных битов, при котором оставшиеся биты остаются нетронутыми. Для формы выбора части допустимы только константные выражения.

-

элемент памяти — одно слово из памяти. Обратите внимание, что битовые выборки и выборочные выборки недопустимы в ссылках на элементы памяти.

-