Очень крупномасштабная интеграция (VLSI) — это процесс создания интегральной схемы (ИС) путем объединения тысяч транзисторов в один чип. СБИС началось в 1970-х годах, когда разрабатывались сложные полупроводниковые и коммуникационные технологии. Микропроцессор является устройством VLSI.

До внедрения технологии VLSI большинство микросхем имели ограниченный набор функций, которые они могли выполнять. Электронная схема может состоять из процессора, ПЗУ, ОЗУ и другой связующей логики . VLSI позволяет разработчикам интегральных схем добавить все это в один чип.

Электронная промышленность достигла феноменального роста за последние несколько десятилетий, главным образом благодаря быстрому прогрессу в области крупномасштабных интеграционных технологий и приложений для проектирования систем. С появлением проектов очень крупномасштабной интеграции (VLSI) число применений интегральных микросхем (ИС) в высокопроизводительных вычислениях, средствах управления, телекоммуникациях, обработке изображений и видео, а также бытовой электронике растет очень быстрыми темпами.

Современные передовые технологии, такие как видео и сотовая связь с высоким разрешением и низкой скоростью передачи битов, обеспечивают конечным пользователям изумительное количество приложений, вычислительную мощность и мобильность. Ожидается, что эта тенденция будет быстро развиваться, что будет иметь очень важное значение для проектирования СБИС и систем.

VLSI Design Flow

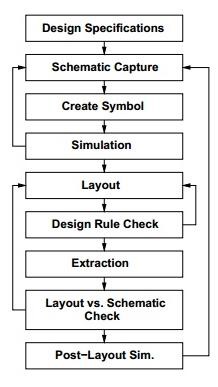

Схема проектирования микросхем СБИС показана на рисунке ниже. Различные уровни дизайна пронумерованы, и блоки показывают процессы в процессе проектирования.

Сначала идут спецификации, они описывают абстрактно, функциональность, интерфейс и архитектуру цифровой схемы IC, которая будет разработана.

Затем создается поведенческое описание для анализа дизайна с точки зрения функциональности, производительности, соответствия заданным стандартам и других спецификаций.

Описание RTL выполняется с использованием HDL. Это описание RTL моделируется для проверки функциональности. С этого момента нам нужна помощь инструментов EDA.

Затем описание RTL преобразуется в список соединений уровня шлюза с использованием инструментов логического синтеза. Список соединений уровня шлюза — это описание схемы в терминах затворов и соединений между ними, которые выполнены таким образом, что они соответствуют характеристикам синхронизации, мощности и площади.

Наконец, создается физический макет, который будет проверен и затем отправлен на изготовление.

Y Диаграмма

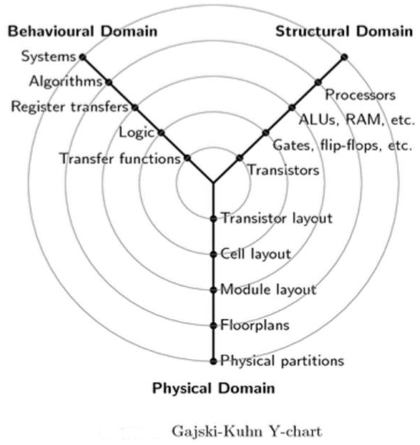

Y-диаграмма Гайски-Куна — это модель, которая учитывает соображения при разработке полупроводниковых приборов.

Три области Y-диаграммы Гайски-Куна находятся на радиальных осях. Каждый из доменов можно разделить на уровни абстракции, используя концентрические кольца.

На верхнем уровне (внешнее кольцо) мы рассмотрим архитектуру чипа; на нижних уровнях (внутренние кольца) мы последовательно совершенствуем проект до более детальной реализации —

Создание структурного описания из поведенческого достигается посредством процессов синтеза высокого уровня или логического синтеза.

Создание физического описания из структурного достигается путем синтеза макета.

Иерархия проектирования — Структурная

Иерархия дизайна включает в себя принцип «Разделяй и властвуй». Это не что иное, как деление задачи на более мелкие задачи, пока она не достигнет своего простейшего уровня. Этот процесс является наиболее подходящим, потому что последнее развитие дизайна стало настолько простым, что его изготовление стало легче.

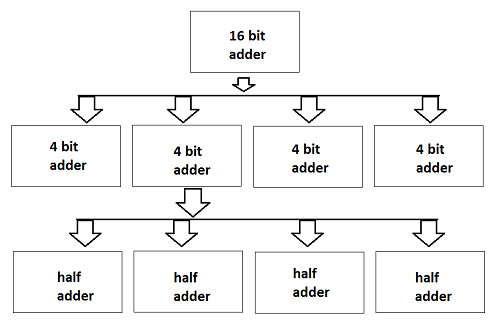

Мы можем спроектировать данную задачу в область процесса проектирования (Поведенческий, Структурный и Геометрический). Чтобы понять это, давайте рассмотрим пример проектирования 16-разрядного сумматора, как показано на рисунке ниже.

Здесь весь чип 16-битного сумматора разделен на четыре модуля 4-битных сумматоров. Далее делим 4-битный сумматор на 1-битный сумматор или половину сумматора. Добавление 1 бита является самым простым процессом проектирования, и его внутреннюю схему также легко изготовить на чипе. Теперь, соединив все последние четыре сумматора, мы можем спроектировать 4-битный сумматор и, двигаясь дальше, мы можем спроектировать 16-битный сумматор.