Микропроцессор — Обзор

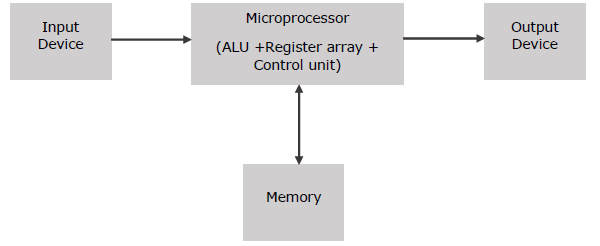

Микропроцессор — это управляющий блок микрокомпьютера, изготовленный на небольшом чипе, способный выполнять операции ALU (Арифметическая логическая единица) и связываться с другими подключенными к нему устройствами.

Микропроцессор состоит из ALU, массива регистров и блока управления. АЛУ выполняет арифметические и логические операции с данными, полученными из памяти или устройства ввода. Массив регистров состоит из регистров, обозначенных буквами, как B, C, D, E, H, L и аккумулятора. Блок управления контролирует поток данных и инструкций внутри компьютера.

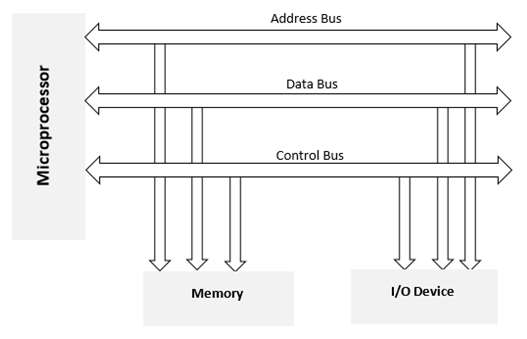

Блок-схема базового микрокомпьютера

Как работает микропроцессор?

Микропроцессор следует последовательности: выборка, декодирование, а затем выполнение.

Первоначально инструкции хранятся в памяти в последовательном порядке. Микропроцессор извлекает эти инструкции из памяти, затем декодирует их и выполняет эти инструкции до тех пор, пока не будет достигнута команда STOP. Позже он отправляет результат в двоичном формате на выходной порт. Между этими процессами регистр временно хранит данные, а ALU выполняет вычислительные функции.

Список терминов, используемых в микропроцессоре

Вот список некоторых часто используемых терминов в микропроцессоре:

-

Набор инструкций — это набор инструкций, которые может понять микропроцессор.

-

Полоса пропускания — это число битов, обрабатываемых в одной инструкции.

-

Тактовая частота — определяет количество операций в секунду, которые может выполнять процессор. Он выражается в мегагерцах (МГц) или гигагерцах (ГГц). Он также известен как тактовая частота.

-

Длина слова — зависит от ширины внутренней шины данных, регистров, ALU и т. Д. 8-разрядный микропроцессор может одновременно обрабатывать 8-разрядные данные. Длина слова варьируется от 4 до 64 бит в зависимости от типа микрокомпьютера.

-

Типы данных — Микропроцессор имеет несколько форматов типов данных, таких как двоичные, BCD, ASCII, числа со знаком и без знака.

Набор инструкций — это набор инструкций, которые может понять микропроцессор.

Полоса пропускания — это число битов, обрабатываемых в одной инструкции.

Тактовая частота — определяет количество операций в секунду, которые может выполнять процессор. Он выражается в мегагерцах (МГц) или гигагерцах (ГГц). Он также известен как тактовая частота.

Длина слова — зависит от ширины внутренней шины данных, регистров, ALU и т. Д. 8-разрядный микропроцессор может одновременно обрабатывать 8-разрядные данные. Длина слова варьируется от 4 до 64 бит в зависимости от типа микрокомпьютера.

Типы данных — Микропроцессор имеет несколько форматов типов данных, таких как двоичные, BCD, ASCII, числа со знаком и без знака.

Особенности микропроцессора

Вот список некоторых из самых выдающихся особенностей любого микропроцессора —

-

Экономически эффективный — микропроцессорные чипы доступны по низким ценам и, как следствие, имеют низкую стоимость.

-

Размер — микропроцессор имеет небольшой размер чипа, поэтому является портативным.

-

Низкое энергопотребление — Микропроцессоры изготавливаются с использованием металлооксидной полупроводниковой технологии, которая имеет низкое энергопотребление.

-

Универсальность — микропроцессоры универсальны, поскольку мы можем использовать один и тот же чип в ряде приложений, конфигурируя программное обеспечение.

-

Надежность — частота отказов IC в микропроцессорах очень низка, поэтому она надежна.

Экономически эффективный — микропроцессорные чипы доступны по низким ценам и, как следствие, имеют низкую стоимость.

Размер — микропроцессор имеет небольшой размер чипа, поэтому является портативным.

Низкое энергопотребление — Микропроцессоры изготавливаются с использованием металлооксидной полупроводниковой технологии, которая имеет низкое энергопотребление.

Универсальность — микропроцессоры универсальны, поскольку мы можем использовать один и тот же чип в ряде приложений, конфигурируя программное обеспечение.

Надежность — частота отказов IC в микропроцессорах очень низка, поэтому она надежна.

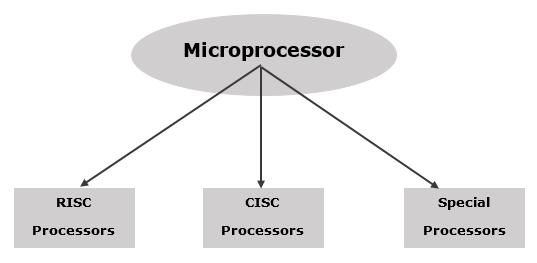

Микропроцессор — Классификация

Микропроцессор можно разделить на три категории —

RISC-процессор

RISC расшифровывается как компьютер с сокращенным набором команд . Он предназначен для сокращения времени выполнения за счет упрощения набора команд компьютера. Используя процессоры RISC, каждая инструкция требует только одного такта для выполнения результатов в единое время выполнения. Это снижает эффективность, так как появляется больше строк кода, поэтому для хранения инструкций требуется больше оперативной памяти. Компилятор также должен работать больше, чтобы преобразовать инструкции языка высокого уровня в машинный код.

Некоторые из процессоров RISC —

- Мощность ПК: 601, 604, 615, 620

- DEC Alpha: 210642, 211066, 21068, 21164

- MIPS: TS (R10000) RISC-процессор

- PA-RISC: HP 7100LC

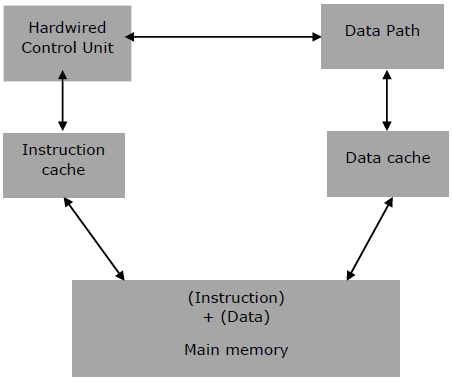

Архитектура РИСК

Микропроцессорная архитектура RISC использует высокооптимизированный набор инструкций. Он используется в портативных устройствах, таких как Apple iPod, благодаря своей энергоэффективности.

Характеристики РИСК

Основные характеристики процессора RISC следующие:

-

Он состоит из простых инструкций.

-

Он поддерживает различные форматы типов данных.

-

Он использует простые режимы адресации и инструкции фиксированной длины для конвейерной обработки.

-

Он поддерживает регистр для использования в любом контексте.

-

Время выполнения одного цикла.

-

Инструкции «LOAD» и «STORE» используются для доступа к ячейке памяти.

-

Он состоит из большего количества регистров.

-

Он состоит из меньшего количества транзисторов.

Он состоит из простых инструкций.

Он поддерживает различные форматы типов данных.

Он использует простые режимы адресации и инструкции фиксированной длины для конвейерной обработки.

Он поддерживает регистр для использования в любом контексте.

Время выполнения одного цикла.

Инструкции «LOAD» и «STORE» используются для доступа к ячейке памяти.

Он состоит из большего количества регистров.

Он состоит из меньшего количества транзисторов.

CISC Процессор

CISC расшифровывается как комплексная компьютерная инструкция . Он предназначен для минимизации количества инструкций на программу, игнорируя количество циклов на инструкцию. Акцент делается на построение сложных инструкций непосредственно в аппаратном обеспечении.

Компилятору приходится выполнять очень мало работы для перевода языка высокого уровня в язык ассемблера / машинный код, поскольку длина кода относительно мала, поэтому для хранения инструкций требуется очень мало ОЗУ.

Некоторые из процессоров CISC —

- IBM 370/168

- VAX 11/780

- Intel 80486

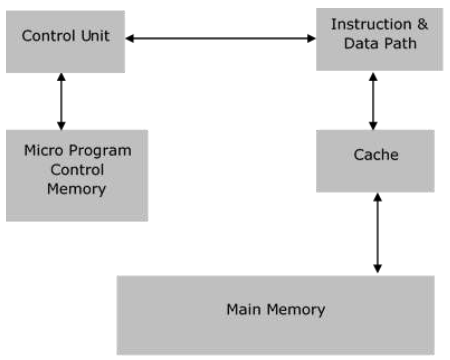

Архитектура CISC

Его архитектура предназначена для уменьшения стоимости памяти, поскольку в больших программах требуется больше места для хранения, что приводит к увеличению стоимости памяти. Чтобы решить эту проблему, количество команд на программу может быть уменьшено путем вложения количества операций в одну инструкцию.

Характеристики CISC

- Разнообразие режимов адресации.

- Большое количество инструкций.

- Переменная длина форматов команд.

- Для выполнения одной инструкции может потребоваться несколько циклов.

- Логика декодирования инструкций сложна.

- Для поддержки нескольких режимов адресации требуется одна инструкция.

Специальные процессоры

Это процессоры, которые предназначены для некоторых специальных целей. Немногие из специальных процессоров кратко обсуждаются —

сопроцессор

Сопроцессор — это специально разработанный микропроцессор, который может выполнять свои функции во много раз быстрее, чем обычный микропроцессор.

Например — Математический сопроцессор.

Некоторые математические сопроцессоры Intel —

- 8087-используется с 8086

- 80287-используется с 80286

- 80387-используется с 80386

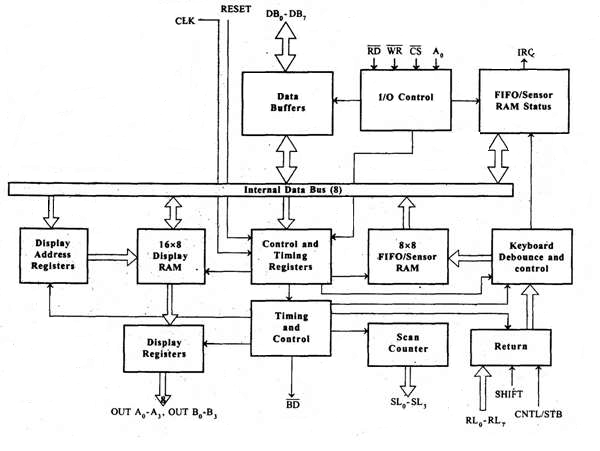

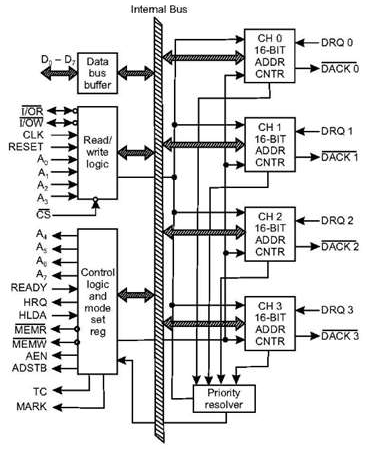

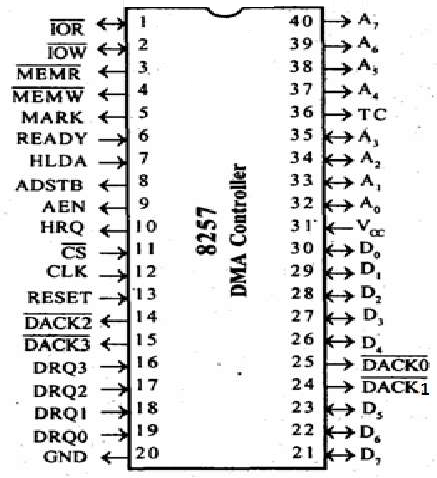

Процессор ввода / вывода

Это специально разработанный микропроцессор с собственной локальной памятью, который используется для управления устройствами ввода-вывода с минимальным участием ЦП.

Например —

- Контроллер прямого доступа к памяти

- Контроллер клавиатуры / мыши

- Контроллер графического дисплея

- Контроллер порта SCSI

Транспутер (Транзистор Компьютер)

Транспьютер — это специально разработанный микропроцессор с собственной локальной памятью и связями для соединения одного транспортера с другим транспортом для межпроцессорной связи. Впервые он был разработан в 1980 году компанией Inmos и нацелен на использование технологии СБИС.

Транспортер может использоваться как однопроцессорная система или может быть подключен к внешним каналам, что снижает стоимость строительства и повышает производительность.

Например — 16-битный T212, 32-битный T425, процессоры с плавающей запятой (T800, T805 и T9000).

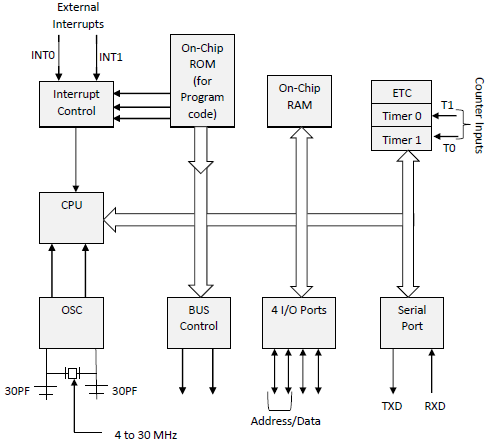

DSP (цифровой сигнальный процессор)

Этот процессор специально разработан для обработки аналоговых сигналов в цифровом виде. Это делается путем выборки уровня напряжения через регулярные промежутки времени и преобразования напряжения в этот момент в цифровую форму. Этот процесс выполняется схемой, называемой аналого-цифровой преобразователь, аналого-цифровой преобразователь или АЦП.

DSP содержит следующие компоненты —

-

Память программ — хранит программы, которые DSP будет использовать для обработки данных.

-

Память данных — хранит информацию для обработки.

-

Compute Engine — выполняет математическую обработку, получая доступ к программе из памяти программ и данным из памяти данных.

-

Ввод / вывод — он подключается к внешнему миру.

Память программ — хранит программы, которые DSP будет использовать для обработки данных.

Память данных — хранит информацию для обработки.

Compute Engine — выполняет математическую обработку, получая доступ к программе из памяти программ и данным из памяти данных.

Ввод / вывод — он подключается к внешнему миру.

Его приложения —

- Синтез звука и музыки

- Аудио и видео компрессия

- Обработка видеосигнала

- 2D и 3D графическое ускорение.

Например — серия TMS 320 от Texas Instrument, например, TMS 320C40, TMS320C50.

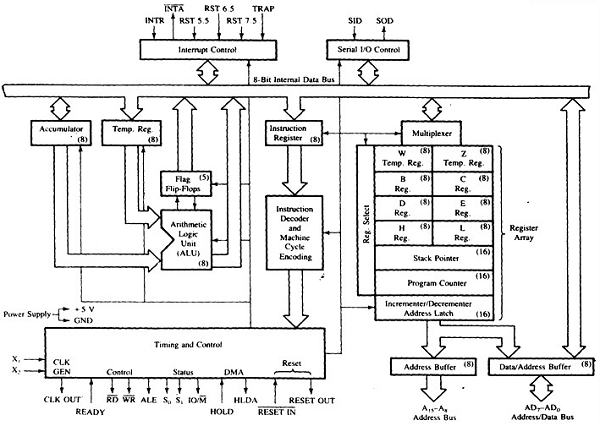

Микропроцессор — 8085 Архитектура

8085 произносится как «восемьдесят восемьдесят пять» микропроцессор. Это 8-битный микропроцессор, разработанный Intel в 1977 году с использованием технологии NMOS.

Он имеет следующую конфигурацию —

- 8-битная шина данных

- 16-битная адресная шина, которая может адресовать до 64 КБ

- 16-битный программный счетчик

- 16-битный указатель стека

- Шесть 8-битных регистров, расположенных попарно: BC, DE, HL

- Требуется питание + 5 В для работы на однофазных тактовых частотах 3,2 МГц

Используется в стиральных машинах, микроволновых печах, мобильных телефонах и т. Д.

Микропроцессор 8085 — Функциональные блоки

8085 состоит из следующих функциональных блоков —

аккумуляторный

Это 8-битный регистр, используемый для выполнения арифметических, логических операций ввода-вывода и загрузки / сохранения. Он подключен к внутренней шине данных и ALU.

Арифметико-логическое устройство

Как следует из названия, он выполняет арифметические и логические операции, такие как сложение, вычитание, AND, OR и т. Д. Над 8-битными данными.

Регистр общего назначения

В процессоре 8085 имеется 6 регистров общего назначения, то есть B, C, D, E, H & L. Каждый регистр может содержать 8-битные данные.

Эти регистры могут работать в паре для хранения 16-битных данных, и их комбинация сочетания похожа на BC, DE & HL.

Счетчик команд

Это 16-битный регистр, используемый для хранения адреса памяти в следующей команде, которая должна быть выполнена. Микропроцессор увеличивает программу всякий раз, когда выполняется инструкция, так что счетчик программы указывает на адрес памяти следующей инструкции, которая будет выполнена.

Указатель стека

Это также 16-битный регистр, работающий как стек, который всегда увеличивается / уменьшается на 2 во время операций push & pop.

Временный регистр

Это 8-битный регистр, который содержит временные данные арифметических и логических операций.

Флаг регистр

Это 8-битный регистр, имеющий пять 1-битных триггеров, которые содержат 0 или 1 в зависимости от результата, сохраненного в аккумуляторе.

Это набор из 5 шлепанцев —

- Приметы)

- Ноль (Z)

- Вспомогательный Carry (AC)

- Паритет (P)

- Нести (С)

Его битовая позиция показана в следующей таблице —

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | Д0 |

|---|---|---|---|---|---|---|---|

| S | Z | переменный ток | п | CY |

Регистр команд и декодер

Это 8-битный регистр. Когда инструкция извлекается из памяти, она сохраняется в регистре команд. Декодер команд декодирует информацию, представленную в регистре команд.

Сроки и блок управления

Он обеспечивает синхронизацию и управляющий сигнал для микропроцессора для выполнения операций. Ниже приведены сигналы синхронизации и управления, которые управляют внешними и внутренними цепями.

- Управляющие сигналы: ГОТОВ, RD ‘, WR’, ALE

- Сигналы состояния: S0, S1, IO / M ‘

- Сигналы DMA: ДЕРЖАТЬ, HLDA

- Сигналы RESET: RESET IN, RESET OUT

Управление прерываниями

Как следует из названия, он контролирует прерывания во время процесса. Когда микропроцессор выполняет основную программу и всякий раз, когда происходит прерывание, микропроцессор переносит управление из основной программы для обработки входящего запроса. После завершения запроса управление возвращается к основной программе.

В микропроцессоре 8085 имеется 5 сигналов прерывания: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

Управление последовательным вводом / выводом

Он управляет последовательной передачей данных с помощью этих двух инструкций: SID (данные последовательного ввода) и SOD (данные последовательного ввода).

Адресный буфер и адресный буфер данных

Содержимое, хранящееся в указателе стека и программном счетчике, загружается в буфер адресов и буфер данных-адресов для связи с ЦП. Микросхемы памяти и ввода / вывода подключены к этим шинам; CPU может обмениваться нужными данными с памятью и чипами ввода / вывода.

Адресная шина и шина данных

Шина данных несет данные для хранения. Он является двунаправленным, тогда как адресная шина переносит место, где она должна храниться, и является однонаправленной. Он используется для передачи данных и адреса устройств ввода-вывода.

8085 Архитектура

Мы попытались изобразить архитектуру 8085 с помощью следующего изображения —

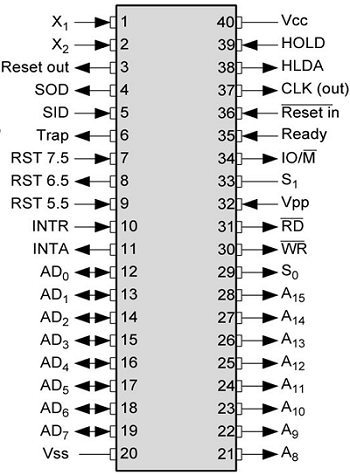

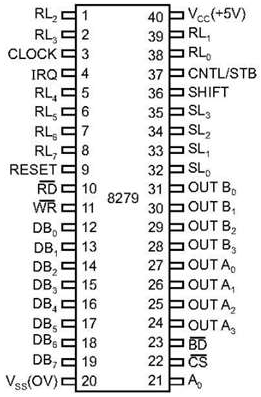

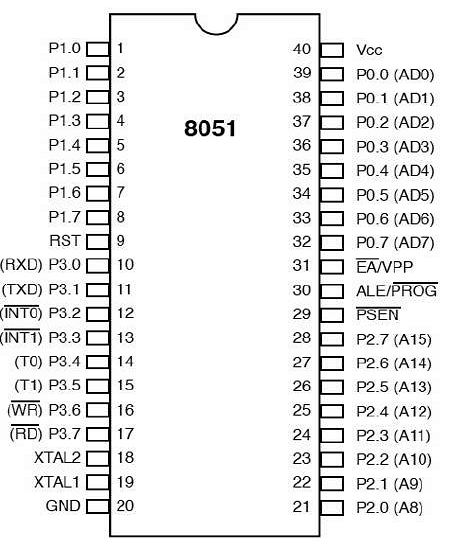

Микропроцессор — 8085 контактов

На следующем рисунке изображена схема контактов микропроцессора 8085 —

Контакты микропроцессора 8085 можно разделить на семь групп:

Адресная шина

A15-A8, он несет самый значительный 8-битный адрес памяти / ввода-вывода.

Шина данных

AD7-AD0, он несет наименее значимый 8-битный адрес и шину данных.

Сигналы управления и состояния

Эти сигналы используются для определения характера операции. Есть 3 сигнала управления и 3 сигнала состояния.

Три управляющих сигнала: RD, WR и ALE.

-

RD — этот сигнал указывает, что выбранное устройство ввода-вывода или запоминающее устройство должно быть прочитано и готово к приему данных, доступных на шине данных.

-

WR — этот сигнал указывает, что данные на шине данных должны быть записаны в выбранную память или место ввода / вывода.

-

ALE — это положительный импульс, генерируемый микропроцессором при запуске новой операции. Когда пульс становится высоким, это указывает на адрес. Когда пульс идет вниз, это указывает на данные.

RD — этот сигнал указывает, что выбранное устройство ввода-вывода или запоминающее устройство должно быть прочитано и готово к приему данных, доступных на шине данных.

WR — этот сигнал указывает, что данные на шине данных должны быть записаны в выбранную память или место ввода / вывода.

ALE — это положительный импульс, генерируемый микропроцессором при запуске новой операции. Когда пульс становится высоким, это указывает на адрес. Когда пульс идет вниз, это указывает на данные.

Три сигнала состояния: IO / M, S0 и S1.

IO / М

Этот сигнал используется для различения операций ввода-вывода и памяти, т. Е. Когда он высокий, это означает работу ввода-вывода, а когда он низкий, то он указывает на работу памяти.

S1 & S0

Эти сигналы используются для определения типа текущей операции.

Источник питания

Есть 2 источника питания — VCC и VSS. VCC указывает источник питания + 5 В, а VSS указывает сигнал заземления.

Тактовые сигналы

Есть 3 тактовых сигнала, то есть X1, X2, CLK OUT.

-

X1, X2 — Кристалл (RC, LC N / W) подключен к этим двум контактам и используется для установки частоты внутреннего тактового генератора. Эта частота внутренне делится на 2.

-

CLK OUT — этот сигнал используется в качестве системных часов для устройств, подключенных к микропроцессору.

X1, X2 — Кристалл (RC, LC N / W) подключен к этим двум контактам и используется для установки частоты внутреннего тактового генератора. Эта частота внутренне делится на 2.

CLK OUT — этот сигнал используется в качестве системных часов для устройств, подключенных к микропроцессору.

Прерывания и внешние сигналы

Прерывания — это сигналы, генерируемые внешними устройствами для запроса микропроцессора на выполнение задачи. Существует 5 сигналов прерывания, т.е. TRAP, RST 7.5, RST 6.5, RST 5.5 и INTR. Мы подробно обсудим прерывания в разделе прерываний.

-

INTA — это сигнал подтверждения прерывания.

-

RESET IN — этот сигнал используется для сброса микропроцессора путем установки счетчика программы на ноль.

-

RESET OUT — этот сигнал используется для сброса всех подключенных устройств при сбросе микропроцессора.

-

ГОТОВ — этот сигнал указывает на то, что устройство готово к отправке или получению данных. Если READY имеет низкий уровень, тогда процессор должен ждать, пока READY поднимется до высокого уровня.

-

HOLD — этот сигнал указывает, что другой мастер запрашивает использование адреса и шин данных.

-

HLDA (HOLD Acknowledge) — указывает на то, что ЦП получил запрос HOLD, и он освободит шину в следующем тактовом цикле. HLDA устанавливается на низкий уровень после снятия сигнала HOLD.

INTA — это сигнал подтверждения прерывания.

RESET IN — этот сигнал используется для сброса микропроцессора путем установки счетчика программы на ноль.

RESET OUT — этот сигнал используется для сброса всех подключенных устройств при сбросе микропроцессора.

ГОТОВ — этот сигнал указывает на то, что устройство готово к отправке или получению данных. Если READY имеет низкий уровень, тогда процессор должен ждать, пока READY поднимется до высокого уровня.

HOLD — этот сигнал указывает, что другой мастер запрашивает использование адреса и шин данных.

HLDA (HOLD Acknowledge) — указывает на то, что ЦП получил запрос HOLD, и он освободит шину в следующем тактовом цикле. HLDA устанавливается на низкий уровень после снятия сигнала HOLD.

Последовательные сигналы ввода / вывода

Есть 2 последовательных сигнала, то есть SID и SOD, и эти сигналы используются для последовательной связи.

-

SOD (строка данных последовательного выхода) — выходной SOD устанавливается / сбрасывается в соответствии с инструкцией SIM.

-

SID (строка последовательного ввода данных) — данные в этой строке загружаются в аккумулятор при каждом выполнении команды RIM.

SOD (строка данных последовательного выхода) — выходной SOD устанавливается / сбрасывается в соответствии с инструкцией SIM.

SID (строка последовательного ввода данных) — данные в этой строке загружаются в аккумулятор при каждом выполнении команды RIM.

8085 адресация режимов и прерываний

Теперь давайте обсудим режимы адресации в микропроцессоре 8085.

Режимы адресации в 8085 году

Это инструкции, используемые для передачи данных из одного регистра в другой регистр, из памяти в регистр и из регистра в память без каких-либо изменений в содержимом. Режимы адресации в 8085 году подразделяются на 5 групп —

Режим немедленной адресации

В этом режиме 8/16-битные данные указываются в самой инструкции как один из ее операндов. Например: MVI K, 20F: означает, что 20F скопирован в регистр K.

Зарегистрировать режим адресации

В этом режиме данные копируются из одного регистра в другой. Например: MOV K, B: означает, что данные в регистре B копируются в регистр K.

Режим прямой адресации

В этом режиме данные напрямую копируются с заданного адреса в регистр. Например: LDB 5000K: означает, что данные по адресу 5000K копируются в регистр B.

Режим косвенной адресации

В этом режиме данные передаются из одного регистра в другой, используя адрес, указанный регистром. Например: MOV K, B: означает, что данные передаются с адреса памяти, указанного регистром, в регистр K.

Подразумеваемый режим адресации

Этот режим не требует никакого операнда; данные определяются самим кодом операции. Например: CMP.

Прерывает в 8085

Прерывания — это сигналы, генерируемые внешними устройствами для запроса микропроцессора для выполнения задачи. Существует 5 сигналов прерывания, т.е. TRAP, RST 7.5, RST 6.5, RST 5.5 и INTR.

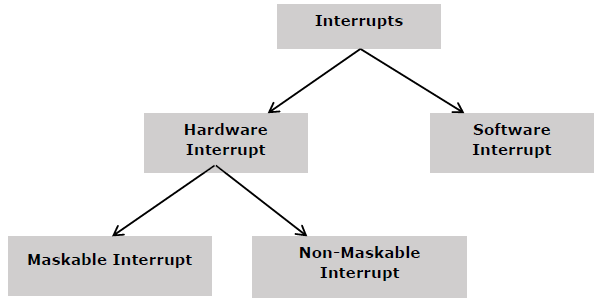

Прерывания классифицируются на следующие группы в зависимости от их параметра —

-

Векторное прерывание — в этом типе прерывания адрес прерывания известен процессору. Например: RST7.5, RST6.5, RST5.5, TRAP.

-

Невекторное прерывание — В этом типе прерывания адрес прерывания не известен процессору, поэтому для прерывания адрес прерывания должен отправляться внешним устройством. Например: INTR.

-

Маскируемое прерывание — в этом типе прерывания мы можем отключить прерывание, написав некоторые инструкции в программу. Например: RST7.5, RST6.5, RST5.5.

-

Немаскируемое прерывание — в этом типе прерывания мы не можем отключить прерывание, записав некоторые инструкции в программу. Например: TRAP.

-

Программное прерывание. В этом типе прерывания программист должен добавить в программу инструкции для выполнения прерывания. В 8085 есть 8 программных прерываний, то есть RST0, RST1, RST2, RST3, RST4, RST5, RST6 и RST7.

-

Аппаратное прерывание. В 8085 в качестве аппаратных прерываний используются 5 контактов прерывания, т. Е. TRAP, RST7.5, RST6.5, RST5.5, INTA.

Векторное прерывание — в этом типе прерывания адрес прерывания известен процессору. Например: RST7.5, RST6.5, RST5.5, TRAP.

Невекторное прерывание — В этом типе прерывания адрес прерывания не известен процессору, поэтому для прерывания адрес прерывания должен отправляться внешним устройством. Например: INTR.

Маскируемое прерывание — в этом типе прерывания мы можем отключить прерывание, написав некоторые инструкции в программу. Например: RST7.5, RST6.5, RST5.5.

Немаскируемое прерывание — в этом типе прерывания мы не можем отключить прерывание, записав некоторые инструкции в программу. Например: TRAP.

Программное прерывание. В этом типе прерывания программист должен добавить в программу инструкции для выполнения прерывания. В 8085 есть 8 программных прерываний, то есть RST0, RST1, RST2, RST3, RST4, RST5, RST6 и RST7.

Аппаратное прерывание. В 8085 в качестве аппаратных прерываний используются 5 контактов прерывания, т. Е. TRAP, RST7.5, RST6.5, RST5.5, INTA.

Примечание. NTA не является прерыванием, оно используется микропроцессором для отправки подтверждения. TRAP имеет самый высокий приоритет, затем RST7.5 и так далее.

Программа обработки прерываний (ISR)

Небольшая программа или подпрограмма, которая при выполнении обслуживает соответствующий источник прерывания, называется ISR.

TRAP

Это немаскируемое прерывание, имеющее самый высокий приоритет среди всех прерываний. По умолчанию он включен, пока не получит подтверждение. В случае сбоя он выполняется как ISR и отправляет данные в резервную память. Это прерывание передает управление в местоположение 0024H.

RST7.5

Это маскируемое прерывание, имеющее второй по приоритетности приоритет среди всех прерываний. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит на адрес 003CH.

RST 6.5

Это маскируемое прерывание, имеющее третий самый высокий приоритет среди всех прерываний. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит по адресу 0034H.

RST 5.5

Это маскируемое прерывание. Когда выполняется это прерывание, процессор сохраняет содержимое регистра ПК в стек и переходит по адресу 002CH.

ВВЕДЕНИ

Это маскируемое прерывание, имеющее самый низкий приоритет среди всех прерываний. Его можно отключить путем сброса микропроцессора.

Когда сигнал INTR становится высоким , могут произойти следующие события:

-

Микропроцессор проверяет состояние сигнала INTR во время выполнения каждой инструкции.

-

Когда сигнал INTR высокий, микропроцессор завершает свою текущую команду и посылает активный сигнал подтверждения прерывания низкого уровня.

-

Когда инструкции получены, микропроцессор сохраняет адрес следующей инструкции в стеке и выполняет полученную инструкцию.

Микропроцессор проверяет состояние сигнала INTR во время выполнения каждой инструкции.

Когда сигнал INTR высокий, микропроцессор завершает свою текущую команду и посылает активный сигнал подтверждения прерывания низкого уровня.

Когда инструкции получены, микропроцессор сохраняет адрес следующей инструкции в стеке и выполняет полученную инструкцию.

Микропроцессор — 8085 инструкций

Давайте посмотрим на программирование микропроцессора 8085.

Наборы инструкций — это коды команд для выполнения некоторых задач. Он классифицируется на пять категорий.

| S.No. | Инструкция и описание |

|---|---|

| 1 | Инструкция по управлению

Ниже приведена таблица со списком команд управления с их значениями. |

| 2 | Логические Инструкции

Ниже приведена таблица со списком логических инструкций с их значениями. |

| 3 | Инструкции по ветвлению

Ниже приведена таблица со списком команд ветвления с их значениями. |

| 4 | Арифметические инструкции

Ниже приведена таблица со списком арифметических инструкций с их значениями. |

| 5 | Инструкция по передаче данных

Ниже приведена таблица со списком команд передачи данных с их значениями. |

Ниже приведена таблица со списком команд управления с их значениями.

Ниже приведена таблица со списком логических инструкций с их значениями.

Ниже приведена таблица со списком команд ветвления с их значениями.

Ниже приведена таблица со списком арифметических инструкций с их значениями.

Ниже приведена таблица со списком команд передачи данных с их значениями.

8085 — Демонстрационные программы

Теперь давайте посмотрим на некоторые демонстрации программ, используя приведенные выше инструкции:

Добавление двух 8-битных чисел

Напишите программу для добавления данных в ячейку памяти 3005H и 3006H и сохраните результат в ячейке памяти 3007H.

Проблема демо —

(3005H) = 14H (3006H) = 89H

Результат —

14H + 89H = 9DH

Код программы можно записать так:

LXI H 3005H: «HL points 3005H» MOV A, M: «Получение первого операнда» INX H: «HL points 3006H» ДОБАВИТЬ М: «Добавить второй операнд» INX H: "HL points 3007H" MOV M, A: «Сохранить результат на 3007H» HLT: «Программа выхода»

Обмен местами памяти

Напишите программу для обмена данными в 5000M и 6000M памяти.

LDA 5000M : "Getting the contents at5000M location into accumulator" MOV B, A : "Save the contents into B register" LDA 6000M : "Getting the contents at 6000M location into accumulator" STA 5000M : "Store the contents of accumulator at address 5000M" MOV A, B : "Get the saved contents back into A register" STA 6000M : "Store the contents of accumulator at address 6000M"

Упорядочить числа в порядке возрастания

Напишите программу, чтобы расположить первые 10 чисел с адреса памяти 3000H в порядке возрастания.

MVI B, 09 :"Initialize counter" START :"LXI H, 3000H: Initialize memory pointer" MVI C, 09H :"Initialize counter 2" BACK: MOV A, M :"Get the number" INX H :"Increment memory pointer" CMP M :"Compare number with next number" JC SKIP :"If less, don’t interchange" JZ SKIP :"If equal, don’t interchange" MOV D, M MOV M, A DCX H MOV M, D INX H :"Interchange two numbers" SKIP:DCR C :"Decrement counter 2" JNZ BACK :"If not zero, repeat" DCR B :"Decrement counter 1" JNZ START HLT :"Terminate program execution"

Микропроцессор — 8086 Обзор

Микропроцессор 8086 — это расширенная версия микропроцессора 8085, разработанная Intel в 1976 году. Это 16-разрядный микропроцессор с 20 адресными строками и 16 строками данных, который обеспечивает хранение до 1 МБ. Он состоит из мощного набора команд, который позволяет легко выполнять такие операции, как умножение и деление.

Он поддерживает два режима работы, то есть Максимальный режим и Минимальный режим. Режим Maximum подходит для системы с несколькими процессорами, а режим Minimum подходит для системы с одним процессором.

Особенности 8086

Наиболее характерные особенности микропроцессора 8086:

-

Он имеет очередь команд, которая способна хранить шесть байтов инструкций из памяти, что приводит к более быстрой обработке.

-

Это был первый 16-битный процессор с 16-битным ALU, 16-битными регистрами, внутренней шиной данных и 16-битной внешней шиной данных, что привело к более быстрой обработке.

-

Это доступно в 3 версиях, основанных на частоте операции —

-

8086 → 5 МГц

-

8086-2 → 8 МГц

-

(c) 8086-1 → 10 МГц

-

-

Он использует два этапа конвейерной обработки: этап извлечения и этап выполнения, что повышает производительность.

-

Этап выборки может выполнять предварительную выборку до 6 байтов инструкций и сохранять их в очереди.

-

Этап выполнения выполняет эти инструкции.

-

Имеет 256 векторных прерываний.

-

Он состоит из 29 000 транзисторов.

Он имеет очередь команд, которая способна хранить шесть байтов инструкций из памяти, что приводит к более быстрой обработке.

Это был первый 16-битный процессор с 16-битным ALU, 16-битными регистрами, внутренней шиной данных и 16-битной внешней шиной данных, что привело к более быстрой обработке.

Это доступно в 3 версиях, основанных на частоте операции —

8086 → 5 МГц

8086-2 → 8 МГц

(c) 8086-1 → 10 МГц

Он использует два этапа конвейерной обработки: этап извлечения и этап выполнения, что повышает производительность.

Этап выборки может выполнять предварительную выборку до 6 байтов инструкций и сохранять их в очереди.

Этап выполнения выполняет эти инструкции.

Имеет 256 векторных прерываний.

Он состоит из 29 000 транзисторов.

Сравнение микропроцессора 8085 и 8086

-

Размер — 8085 — это 8-битный микропроцессор, тогда как 8086 — это 16-битный микропроцессор.

-

Адресная шина — 8085 имеет 16-разрядную адресную шину, а 8086 имеет 20-разрядную адресную шину.

-

Память — 8085 может получить доступ до 64 КБ, а 8086 — до 1 МБ памяти.

-

Инструкция — 8085 не имеет очереди команд, тогда как 8086 имеет очередь команд.

-

Конвейерная обработка — 8085 не поддерживает конвейерную архитектуру, в то время как 8086 поддерживает конвейерную архитектуру.

-

I / O — 8085 может адресовать 2 ^ 8 = 256 I / O, тогда как 8086 может обращаться к 2 ^ 16 = 65 536 I / O.

-

Стоимость — стоимость 8085 низкая, а 8086 высокая.

Размер — 8085 — это 8-битный микропроцессор, тогда как 8086 — это 16-битный микропроцессор.

Адресная шина — 8085 имеет 16-разрядную адресную шину, а 8086 имеет 20-разрядную адресную шину.

Память — 8085 может получить доступ до 64 КБ, а 8086 — до 1 МБ памяти.

Инструкция — 8085 не имеет очереди команд, тогда как 8086 имеет очередь команд.

Конвейерная обработка — 8085 не поддерживает конвейерную архитектуру, в то время как 8086 поддерживает конвейерную архитектуру.

I / O — 8085 может адресовать 2 ^ 8 = 256 I / O, тогда как 8086 может обращаться к 2 ^ 16 = 65 536 I / O.

Стоимость — стоимость 8085 низкая, а 8086 высокая.

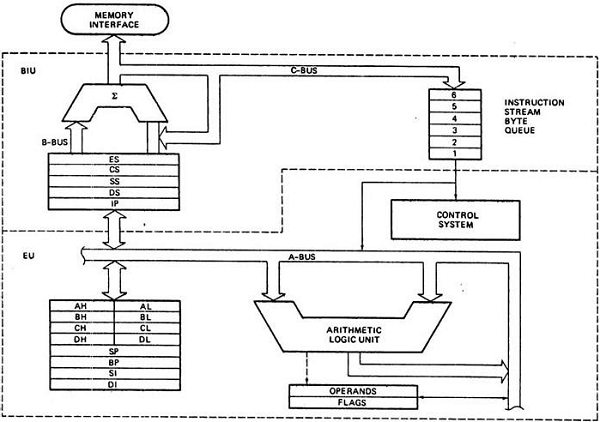

Архитектура 8086 года

Следующая диаграмма изображает архитектуру микропроцессора 8086 —

Микропроцессор — 8086 функциональных блоков

Микропроцессор 8086 разделен на два функциональных блока: EU (исполнительный модуль) и BIU (шинный интерфейсный модуль).

ЕС (исполнительный блок)

Блок выполнения дает инструкции для BIU, в которых указывается, откуда следует извлечь данные, а затем декодировать и выполнять эти инструкции. Его функция заключается в управлении операциями с данными с использованием декодера команд и ALU. EU не имеет прямого соединения с системными шинами, как показано на рисунке выше, он выполняет операции над данными через BIU.

Давайте теперь обсудим функциональные части 8086 микропроцессоров.

ALU

Он обрабатывает все арифметические и логические операции, такие как операции +, -, ×, /, OR, AND, NOT.

Флаг Регистр

Это 16-битный регистр, который ведет себя как триггер, то есть он меняет свое состояние в соответствии с результатом, сохраненным в аккумуляторе. У этого есть 9 флагов, и они разделены на 2 группы — Условные Флаги и Контрольные Флаги.

Условные флаги

Он представляет результат последней выполненной арифметической или логической инструкции. Ниже приведен список условных флагов —

-

Флаг переноса — этот флаг указывает условие переполнения для арифметических операций.

-

Вспомогательный флаг — Когда операция выполняется в ALU, это приводит к переносу / кургану от нижнего полубайта (то есть D0 — D3) к верхнему полубайту (то есть D4 — D7), тогда этот флаг устанавливается, то есть перенос, данный битом D3 для D4 — флаг AF. Процессор использует этот флаг для выполнения двоичного преобразования в BCD.

-

Флаг четности — этот флаг используется для указания четности результата, т. Е. Когда младшие 8 битов результата содержат четное число единиц, устанавливается флаг четности. Для нечетного числа 1 флаг четности сбрасывается.

-

Флаг нуля — этот флаг равен 1, если результат арифметической или логической операции равен нулю, в противном случае он равен 0.

-

Флаг знака — этот флаг содержит знак результата, т. Е. Когда результат операции отрицательный, тогда флаг знака устанавливается в 1, а в 0.

-

Флаг переполнения — этот флаг представляет результат при превышении емкости системы.

Флаг переноса — этот флаг указывает условие переполнения для арифметических операций.

Вспомогательный флаг — Когда операция выполняется в ALU, это приводит к переносу / кургану от нижнего полубайта (то есть D0 — D3) к верхнему полубайту (то есть D4 — D7), тогда этот флаг устанавливается, то есть перенос, данный битом D3 для D4 — флаг AF. Процессор использует этот флаг для выполнения двоичного преобразования в BCD.

Флаг четности — этот флаг используется для указания четности результата, т. Е. Когда младшие 8 битов результата содержат четное число единиц, устанавливается флаг четности. Для нечетного числа 1 флаг четности сбрасывается.

Флаг нуля — этот флаг равен 1, если результат арифметической или логической операции равен нулю, в противном случае он равен 0.

Флаг знака — этот флаг содержит знак результата, т. Е. Когда результат операции отрицательный, тогда флаг знака устанавливается в 1, а в 0.

Флаг переполнения — этот флаг представляет результат при превышении емкости системы.

Контрольные Флаги

Флаги управления управляют операциями исполнительного блока. Ниже приведен список контрольных флагов —

-

Флаг прерывания — используется для одноэтапного управления и позволяет пользователю выполнять одну инструкцию за один раз для отладки. Если он установлен, то программа может быть запущена в одношаговом режиме.

-

Флаг прерывания — это флаг включения / отключения прерывания, то есть используемый для разрешения / запрета прерывания программы. Он установлен в 1 для состояния разрешения прерывания и в 0 для условия отключения прерывания.

-

Флаг направления — используется в строковой операции. Как следует из названия, когда оно установлено, к строковым байтам обращаются от старшего адреса памяти к младшему адресу памяти и наоборот.

Флаг прерывания — используется для одноэтапного управления и позволяет пользователю выполнять одну инструкцию за один раз для отладки. Если он установлен, то программа может быть запущена в одношаговом режиме.

Флаг прерывания — это флаг включения / отключения прерывания, то есть используемый для разрешения / запрета прерывания программы. Он установлен в 1 для состояния разрешения прерывания и в 0 для условия отключения прерывания.

Флаг направления — используется в строковой операции. Как следует из названия, когда оно установлено, к строковым байтам обращаются от старшего адреса памяти к младшему адресу памяти и наоборот.

Регистр общего назначения

Существует 8 регистров общего назначения: AH, AL, BH, BL, CH, CL, DH и DL. Эти регистры могут использоваться отдельно для хранения 8-битных данных и могут использоваться парами для хранения 16-битных данных. Допустимые регистровые пары: AH и AL, BH и BL, CH и CL, а также DH и DL. Это относится к AX, BX, CX и DX соответственно.

-

Регистр AX — Он также известен как регистр аккумулятора. Он используется для хранения операндов для арифметических операций.

-

Регистр BX — используется в качестве базового регистра. Он используется для хранения начального базового адреса области памяти в сегменте данных.

-

Регистр CX — он называется счетчиком. Он используется в инструкции цикла для хранения счетчика цикла.

-

Регистр DX — этот регистр используется для хранения адреса порта ввода / вывода для команды ввода / вывода.

Регистр AX — Он также известен как регистр аккумулятора. Он используется для хранения операндов для арифметических операций.

Регистр BX — используется в качестве базового регистра. Он используется для хранения начального базового адреса области памяти в сегменте данных.

Регистр CX — он называется счетчиком. Он используется в инструкции цикла для хранения счетчика цикла.

Регистр DX — этот регистр используется для хранения адреса порта ввода / вывода для команды ввода / вывода.

Регистр указателя стека

Это 16-битный регистр, который содержит адрес от начала сегмента до ячейки памяти, где слово было недавно сохранено в стеке.

BIU (блок шинного интерфейса)

BIU заботится обо всех передачах данных и адресов по шинам для ЕС, таких как отправка адресов, извлечение инструкций из памяти, чтение данных из портов и памяти, а также запись данных в порты и память. ЕС не имеет направления связи с системными автобусами, так что это возможно с BIU. ЕС и BIU связаны с внутренней шиной.

Он имеет следующие функциональные части —

-

Очередь инструкций — BIU содержит очередь инструкций. BIU получает до 6 байтов следующих инструкций и сохраняет их в очереди инструкций. Когда EU выполняет инструкции и готов к их следующей инструкции, он просто читает инструкцию из этой очереди команд, что приводит к увеличению скорости выполнения.

-

Выборка следующей инструкции во время выполнения текущей инструкции называется конвейерной обработкой .

-

Сегментный регистр — BIU имеет 4 сегментных шины, то есть CS, DS, SS & ES. Он содержит адреса команд и данных в памяти, которые используются процессором для доступа к ячейкам памяти. Он также содержит 1 указатель регистра IP, который содержит адрес следующей инструкции, выполняемой ЕС.

-

CS — это означает сегмент кода. Он используется для адресации области памяти в сегменте кода памяти, где хранится исполняемая программа.

-

DS — это означает сегмент данных. Он состоит из данных, используемых программой и доступных в сегменте данных по адресу смещения или содержимому другого регистра, который содержит адрес смещения.

-

SS — это означает сегмент стека. Он обрабатывает память для хранения данных и адресов во время выполнения.

-

ES — Это означает дополнительный сегмент. ES — это дополнительный сегмент данных, который используется строкой для хранения дополнительных данных назначения.

-

-

Указатель инструкции — это 16-битный регистр, используемый для хранения адреса следующей инструкции, которая должна быть выполнена.

Очередь инструкций — BIU содержит очередь инструкций. BIU получает до 6 байтов следующих инструкций и сохраняет их в очереди инструкций. Когда EU выполняет инструкции и готов к их следующей инструкции, он просто читает инструкцию из этой очереди команд, что приводит к увеличению скорости выполнения.

Выборка следующей инструкции во время выполнения текущей инструкции называется конвейерной обработкой .

Сегментный регистр — BIU имеет 4 сегментных шины, то есть CS, DS, SS & ES. Он содержит адреса команд и данных в памяти, которые используются процессором для доступа к ячейкам памяти. Он также содержит 1 указатель регистра IP, который содержит адрес следующей инструкции, выполняемой ЕС.

CS — это означает сегмент кода. Он используется для адресации области памяти в сегменте кода памяти, где хранится исполняемая программа.

DS — это означает сегмент данных. Он состоит из данных, используемых программой и доступных в сегменте данных по адресу смещения или содержимому другого регистра, который содержит адрес смещения.

SS — это означает сегмент стека. Он обрабатывает память для хранения данных и адресов во время выполнения.

ES — Это означает дополнительный сегмент. ES — это дополнительный сегмент данных, который используется строкой для хранения дополнительных данных назначения.

Указатель инструкции — это 16-битный регистр, используемый для хранения адреса следующей инструкции, которая должна быть выполнена.

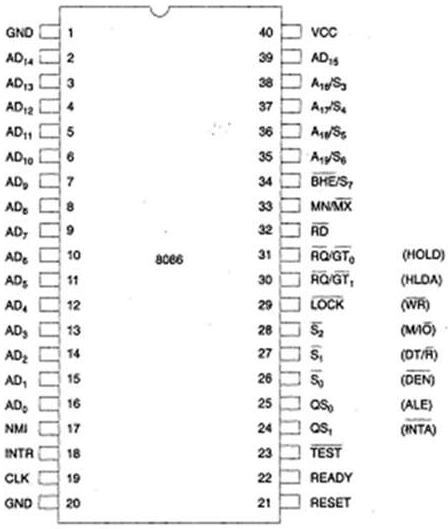

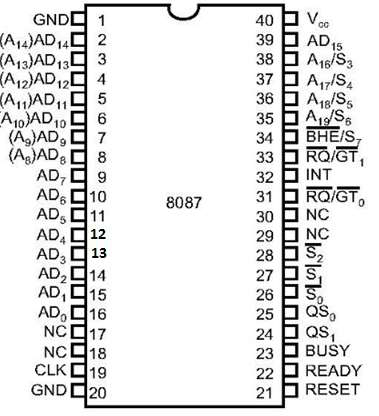

Микропроцессор — 8086 Pin Configuration

8086 был первым 16-разрядным микропроцессором, доступным в 40-контактном DIP (Dual Inline Package) чипе. Теперь давайте подробно обсудим конфигурацию контактов микропроцессора 8086.

8086 Pin Diagram

Вот схема контактов микропроцессора 8086 —

Давайте теперь обсудим сигналы в деталях —

Сигналы питания и частоты

Он использует питание 5 В постоянного тока на выводе V CC 40 и заземление на выводах 1 и 20 V SS для своей работы.

Тактовый сигнал

Тактовый сигнал подается через контакт 19. Он обеспечивает синхронизацию процессора для операций. Его частота различна для разных версий: 5 МГц, 8 МГц и 10 МГц.

Адрес / шина данных

AD0-AD15. Это 16 адрес / шина данных. AD0-AD7 переносит байтовые данные младшего разряда, а AD8AD15 переносит байтовые данные старшего порядка. В течение первого тактового цикла он переносит 16-битный адрес и после этого переносит 16-битные данные.

Адрес / статус шины

A16-A19 / S3-S6. Это 4 адреса / статус шины. В течение первого тактового цикла он несет 4-битный адрес, а затем передает сигналы состояния.

S7 / ППТ

BHE расшифровывается как Bus High Enable. Он доступен на выводе 34 и используется для индикации передачи данных с использованием шины данных D8-D15. Этот сигнал низкий в течение первого тактового цикла, после чего он активен.

Читать ( $ \ overline {RD} $ )

Он доступен на выводе 32 и используется для считывания сигнала для операции чтения.

готовы

Он доступен на выводе 22. Это сигнал подтверждения от устройств ввода-вывода о том, что данные передаются. Это активный высокий сигнал. Когда он высокий, это означает, что устройство готово для передачи данных. Когда оно низкое, это указывает на состояние ожидания.

СБРОС

Он доступен на выводе 21 и используется для возобновления выполнения. Это заставляет процессор немедленно прекратить свою текущую деятельность. Этот сигнал является активным высоким в течение первых 4 тактов для СБРОСА микропроцессора.

ВВЕДЕНИ

Он доступен на выводе 18. Это сигнал запроса прерывания, который дискретизируется в течение последнего тактового цикла каждой команды, чтобы определить, рассматривал ли процессор это как прерывание или нет.

NMI

Он обозначает немаскируемое прерывание и доступен на выводе 17. Это вход, инициируемый фронтом, который вызывает запрос прерывания для микропроцессора.

$ \ Overline {TEST} $

Этот сигнал похож на состояние ожидания и доступен на выводе 23. Когда этот сигнал высокий, то процессор должен ждать состояния IDLE, иначе выполнение продолжается.

MN / $ \ overline {MX} $

Он обозначает Minimum / Maximum и доступен на выводе 33. Он указывает, в каком режиме должен работать процессор; когда он высокий, он работает в минимальном режиме и наоборот.

INTA

Это сигнал подтверждения прерывания и идентификатор, доступный на выводе 24. Когда микропроцессор получает этот сигнал, он подтверждает прерывание.

ALE

Он обозначает защелку разрешения адреса и доступен на выводе 25. Положительный импульс генерируется каждый раз, когда процессор начинает какую-либо операцию. Этот сигнал указывает на наличие действительного адреса в адресной строке / строке данных.

DEN

Он обозначает Data Enable и доступен на выводе 26. Он используется для включения Transreceiver 8286. Transreceiver — это устройство, используемое для отделения данных от адреса / шины данных.

DT / R

Он обозначает сигнал передачи / приема данных и доступен на выводе 27. Он определяет направление потока данных через трансивер. Когда он высокий, данные передаются и наоборот.

М / МО

Этот сигнал используется для различения операций памяти и ввода / вывода. Когда он высокий, это указывает на операцию ввода / вывода, а когда он низкий, указывает на работу памяти. Он доступен на контакте 28.

WR

Он обозначает сигнал записи и доступен на выводе 29. Он используется для записи данных в память или устройство вывода в зависимости от состояния сигнала M / IO.

HLDA

Он обозначает сигнал подтверждения приема и доступен на выводе 30. Этот сигнал подтверждает сигнал HOLD.

ДЕРЖАТЬ

Этот сигнал указывает процессору, что внешние устройства запрашивают доступ к шинам адреса / данных. Он доступен на контакте 31.

QS 1 и QS 0

Это сигналы состояния очереди, которые доступны на контактах 24 и 25. Эти сигналы обеспечивают состояние очереди команд. Их условия показаны в следующей таблице —

| QS 0 | QS 1 | Статус |

|---|---|---|

| 0 | 0 | Нет операции |

| 0 | 1 | Первый байт кода операции из очереди |

| 1 | 0 | Очистить очередь |

| 1 | 1 | Последующий байт из очереди |

S 0 , S 1 , S 2

Это сигналы состояния, которые обеспечивают состояние работы, которое используется контроллером шины 8288 для генерации сигналов управления памятью и вводом / выводом. Они доступны на контактах 26, 27 и 28. Ниже приведена таблица, показывающая их статус —

| S 2 | S 1 | S 0 | Статус |

|---|---|---|---|

| 0 | 0 | 0 | Подтверждение прерывания |

| 0 | 0 | 1 | Чтение ввода / вывода |

| 0 | 1 | 0 | I / O Write |

| 0 | 1 | 1 | стой |

| 1 | 0 | 0 | Извлечение кода операции |

| 1 | 0 | 1 | Чтение памяти |

| 1 | 1 | 0 | Запись в память |

| 1 | 1 | 1 | пассивный |

ЗАМОК

Когда этот сигнал активен, он указывает другим процессорам не просить ЦП покинуть системную шину. Он активируется с помощью префикса LOCK любой инструкции и доступен на выводе 29.

RQ / GT 1 и RQ / GT 0

Это сигналы Запроса / Предоставления, используемые другими процессорами, запрашивающими ЦПУ освободить системную шину. Когда ЦП получает сигнал, он отправляет подтверждение. RQ / GT 0 имеет более высокий приоритет, чем RQ / GT 1 .

Микропроцессор — 8086 инструкционных наборов

Микропроцессор 8086 поддерживает 8 типов инструкций —

- Инструкция по передаче данных

- Арифметические инструкции

- Инструкции по управлению битами

- Строковые Инструкции

- Инструкции по переносу выполнения программы (инструкции по ветвлению и петле)

- Инструкция по управлению процессором

- Инструкции по контролю итерации

- Инструкции по прерыванию

Давайте теперь обсудим эти наборы команд в деталях.

Инструкция по передаче данных

Эти инструкции используются для передачи данных из исходного операнда в целевой операнд. Ниже приведен список инструкций в этой группе —

Инструкция по переводу слова

-

MOV — используется для копирования байта или слова из предоставленного источника в указанное место назначения.

-

PPUSH — используется для размещения слова в верхней части стека.

-

POP — используется для получения слова с вершины стека в указанное место.

-

PUSHA — используется для помещения всех регистров в стек.

-

POPA — используется для получения слов из стека во все регистры.

-

XCHG — используется для обмена данными из двух мест.

-

XLAT — используется для перевода байта в AL с использованием таблицы в памяти.

MOV — используется для копирования байта или слова из предоставленного источника в указанное место назначения.

PPUSH — используется для размещения слова в верхней части стека.

POP — используется для получения слова с вершины стека в указанное место.

PUSHA — используется для помещения всех регистров в стек.

POPA — используется для получения слов из стека во все регистры.

XCHG — используется для обмена данными из двух мест.

XLAT — используется для перевода байта в AL с использованием таблицы в памяти.

Инструкция по переносу портов ввода и вывода

-

IN — используется для чтения байта или слова из предоставленного порта в аккумулятор.

-

OUT — используется для отправки байта или слова из аккумулятора в указанный порт.

IN — используется для чтения байта или слова из предоставленного порта в аккумулятор.

OUT — используется для отправки байта или слова из аккумулятора в указанный порт.

Инструкция по переводу адреса

-

LEA — используется для загрузки адреса операнда в предоставленный регистр.

-

LDS — используется для загрузки регистра DS и другого предоставленного регистра из памяти

-

LES — используется для загрузки регистра ES и другого предоставленного регистра из памяти.

LEA — используется для загрузки адреса операнда в предоставленный регистр.

LDS — используется для загрузки регистра DS и другого предоставленного регистра из памяти

LES — используется для загрузки регистра ES и другого предоставленного регистра из памяти.

Инструкция по передаче флаговых регистров

-

LAHF — используется для загрузки AH младшим байтом регистра флага.

-

SAHF — используется для сохранения регистра AH в младший байт регистра флага.

-

PUSHF — используется для копирования регистра флага в верхней части стека.

-

POPF — используется для копирования слова из верхней части стека в регистр флага.

LAHF — используется для загрузки AH младшим байтом регистра флага.

SAHF — используется для сохранения регистра AH в младший байт регистра флага.

PUSHF — используется для копирования регистра флага в верхней части стека.

POPF — используется для копирования слова из верхней части стека в регистр флага.

Арифметические инструкции

Эти инструкции используются для выполнения арифметических операций, таких как сложение, вычитание, умножение, деление и т. Д.

Ниже приведен список инструкций в этой группе —

Инструкция по выполнению сложения

-

ДОБАВИТЬ — Используется для добавления предоставленного байта в байт / слово в слово.

-

ADC — используется для добавления с переносом.

-

INC — используется для увеличения предоставленного байта / слова на 1.

-

AAA — Используется для настройки ASCII после добавления.

-

DAA — используется для настройки десятичной дроби после операции сложения / вычитания.

ДОБАВИТЬ — Используется для добавления предоставленного байта в байт / слово в слово.

ADC — используется для добавления с переносом.

INC — используется для увеличения предоставленного байта / слова на 1.

AAA — Используется для настройки ASCII после добавления.

DAA — используется для настройки десятичной дроби после операции сложения / вычитания.

Инструкция по выполнению вычитания

-

SUB — Используется для вычитания байта из байта / слова из слова.

-

SBB — Используется для вычитания с заимствованием.

-

DEC — используется для уменьшения предоставленного байта / слова на 1.

-

NPG — Используется для отрицания каждого бита предоставленного байта / слова и добавления дополнения 1/2.

-

CMP — используется для сравнения 2 предоставленных байтов / слов.

-

AAS — Используется для настройки кодов ASCII после вычитания.

-

DAS — используется для настройки десятичной дроби после вычитания.

SUB — Используется для вычитания байта из байта / слова из слова.

SBB — Используется для вычитания с заимствованием.

DEC — используется для уменьшения предоставленного байта / слова на 1.

NPG — Используется для отрицания каждого бита предоставленного байта / слова и добавления дополнения 1/2.

CMP — используется для сравнения 2 предоставленных байтов / слов.

AAS — Используется для настройки кодов ASCII после вычитания.

DAS — используется для настройки десятичной дроби после вычитания.

Инструкция по выполнению умножения

-

MUL — используется для умножения байта без знака на слово / слово за словом.

-

IMUL — используется для умножения подписанного байта за байтом / слово за словом.

-

AAM — используется для настройки кодов ASCII после умножения.

MUL — используется для умножения байта без знака на слово / слово за словом.

IMUL — используется для умножения подписанного байта за байтом / слово за словом.

AAM — используется для настройки кодов ASCII после умножения.

Инструкция по выполнению деления

-

DIV — Используется для деления беззнакового слова по байту или без знака двойного слова по слову.

-

IDIV — Используется для деления подписанного слова в байтах или подписанного двойного слова в слово.

-

AAD — используется для настройки кодов ASCII после деления.

-

CBW — используется для заполнения старшего байта слова копиями знакового бита младшего байта.

-

CWD — используется для заполнения верхнего слова двойного слова знаковым битом нижнего слова.

DIV — Используется для деления беззнакового слова по байту или без знака двойного слова по слову.

IDIV — Используется для деления подписанного слова в байтах или подписанного двойного слова в слово.

AAD — используется для настройки кодов ASCII после деления.

CBW — используется для заполнения старшего байта слова копиями знакового бита младшего байта.

CWD — используется для заполнения верхнего слова двойного слова знаковым битом нижнего слова.

Инструкции по управлению битами

Эти инструкции используются для выполнения операций, в которых задействованы биты данных, например, таких как логические операции, сдвиг и т. Д.

Ниже приведен список инструкций в этой группе —

Инструкция по выполнению логической операции

-

НЕ — используется для инвертирования каждого бита или слова.

-

И — Используется для добавления каждого бита в байте / слове с соответствующим битом в другом байте / слове.

-

ИЛИ — Используется для умножения каждого бита в байте / слове на соответствующий бит в другом байте / слове.

-

XOR — используется для выполнения операции Exclusive-OR над каждым битом в байте / слове с соответствующим битом в другом байте / слове.

-

TEST — используется для добавления операндов для обновления флагов, без влияния на операнды.

НЕ — используется для инвертирования каждого бита или слова.

И — Используется для добавления каждого бита в байте / слове с соответствующим битом в другом байте / слове.

ИЛИ — Используется для умножения каждого бита в байте / слове на соответствующий бит в другом байте / слове.

XOR — используется для выполнения операции Exclusive-OR над каждым битом в байте / слове с соответствующим битом в другом байте / слове.

TEST — используется для добавления операндов для обновления флагов, без влияния на операнды.

Инструкция по выполнению сменных операций

-

SHL / SAL — используется для сдвига битов байта / слова влево и установки нуля (S) в младших битах.

-

SHR — используется для сдвига битов байта / слова вправо и установки нуля (S) в старших битах.

-

SAR — используется для сдвига битов байта / слова вправо и копирования старого MSB в новый MSB.

SHL / SAL — используется для сдвига битов байта / слова влево и установки нуля (S) в младших битах.

SHR — используется для сдвига битов байта / слова вправо и установки нуля (S) в старших битах.

SAR — используется для сдвига битов байта / слова вправо и копирования старого MSB в новый MSB.

Инструкции для выполнения операций поворота

-

ROL — Используется для поворота битов байта / слова влево, то есть от MSB к LSB и к сигналу переноса [CF].

-

ROR — используется для поворота битов байта / слова вправо, то есть от LSB к MSB и к сигналу переноса [CF].

-

RCR — используется для поворота битов байта / слова вправо, то есть от LSB к CF и CF к MSB.

-

RCL — используется для поворота битов байта / слова влево, то есть от MSB к CF и от CF к LSB.

ROL — Используется для поворота битов байта / слова влево, то есть от MSB к LSB и к сигналу переноса [CF].

ROR — используется для поворота битов байта / слова вправо, то есть от LSB к MSB и к сигналу переноса [CF].

RCR — используется для поворота битов байта / слова вправо, то есть от LSB к CF и CF к MSB.

RCL — используется для поворота битов байта / слова влево, то есть от MSB к CF и от CF к LSB.

Строковые Инструкции

Строка — это группа байтов / слов, и их память всегда выделяется в последовательном порядке.

Ниже приведен список инструкций в этой группе —

-

REP — Используется для повторения данной инструкции до CX ≠ 0.

-

REPE / REPZ — Используется для повторения данной инструкции до тех пор, пока CX = 0 или нулевой флаг ZF = 1.

-

REPNE / REPNZ — используется для повторения данной инструкции до тех пор, пока CX = 0 или нулевой флаг ZF = 1.

-

MOVS / MOVSB / MOVSW — используется для перемещения байта / слова из одной строки в другую.

-

COMS / COMPSB / COMPSW — используется для сравнения двух строковых байтов / слов.

-

INS / INSB / INSW — используется в качестве входной строки / байта / слова из порта ввода-вывода в указанное место памяти.

-

OUTS / OUTSB / OUTSW — используется в качестве выходной строки / байта / слова из предоставленной ячейки памяти в порт ввода / вывода.

-

SCAS / SCASB / SCASW — Используется для сканирования строки и сравнения ее байта с байтом в AL или слова строки со словом в AX.

-

LODS / LODSB / LODSW — используется для сохранения байта строки в AL или слова строки в AX.

REP — Используется для повторения данной инструкции до CX ≠ 0.

REPE / REPZ — Используется для повторения данной инструкции до тех пор, пока CX = 0 или нулевой флаг ZF = 1.

REPNE / REPNZ — используется для повторения данной инструкции до тех пор, пока CX = 0 или нулевой флаг ZF = 1.

MOVS / MOVSB / MOVSW — используется для перемещения байта / слова из одной строки в другую.

COMS / COMPSB / COMPSW — используется для сравнения двух строковых байтов / слов.

INS / INSB / INSW — используется в качестве входной строки / байта / слова из порта ввода-вывода в указанное место памяти.

OUTS / OUTSB / OUTSW — используется в качестве выходной строки / байта / слова из предоставленной ячейки памяти в порт ввода / вывода.

SCAS / SCASB / SCASW — Используется для сканирования строки и сравнения ее байта с байтом в AL или слова строки со словом в AX.

LODS / LODSB / LODSW — используется для сохранения байта строки в AL или слова строки в AX.

Инструкции переноса выполнения программы (инструкции ветвления и петли)

Эти инструкции используются для передачи / ветвления команд во время исполнения. Он включает в себя следующие инструкции —

Инструкция по передаче инструкции во время исполнения без каких-либо условий —

-

CALL — используется для вызова процедуры и сохранения адреса возврата в стек.

-

RET — используется для возврата из процедуры в основную программу.

-

JMP — используется для перехода к указанному адресу для перехода к следующей инструкции.

CALL — используется для вызова процедуры и сохранения адреса возврата в стек.

RET — используется для возврата из процедуры в основную программу.

JMP — используется для перехода к указанному адресу для перехода к следующей инструкции.

Инструкция для передачи инструкции во время исполнения с некоторыми условиями —

-

JA / JNBE — Используется для перехода, если выполнено указание выше / не ниже / равно.

-

JAE / JNB — используется для перехода, если инструкция выше / не ниже удовлетворяет.

-

JBE / JNA — Используется для перехода, если инструкция ниже / равно / не выше удовлетворяет.

-

JC — используется для прыжка, если флаг переноса CF = 1

-

JE / JZ — используется для перехода, если равен / ноль флаг ZF = 1

-

JG / JNLE — используется для перехода, если инструкция больше / не меньше / равна.

-

JGE / JNL — используется для перехода, если выполнено больше / равно / не меньше, чем инструкция.

-

JL / JNGE — используется для перехода, если удовлетворяется инструкция меньше / не больше / равно.

-

JLE / JNG — используется для перехода, если выполнено меньше / равно / если не больше, чем инструкция.

-

JNC — используется для прыжка, если нет флага переноса (CF = 0)

-

JNE / JNZ — используется для перехода, если не равен / нулевой флаг ZF = 0

-

JNO — используется для перехода, если нет флага переполнения OF = 0

-

JNP / JPO — используется для перехода, если не четность / четность нечетная PF = 0

-

JNS — используется для прыжка, если не знак SF = 0

-

JO — используется для перехода, если флаг переполнения OF = 1

-

JP / JPE — используется для перехода, если четность / четность даже PF = 1

-

JS — Используется для перехода, если флаг знака SF = 1

JA / JNBE — Используется для перехода, если выполнено указание выше / не ниже / равно.

JAE / JNB — используется для перехода, если инструкция выше / не ниже удовлетворяет.

JBE / JNA — Используется для перехода, если инструкция ниже / равно / не выше удовлетворяет.

JC — используется для прыжка, если флаг переноса CF = 1

JE / JZ — используется для перехода, если равен / ноль флаг ZF = 1

JG / JNLE — используется для перехода, если инструкция больше / не меньше / равна.

JGE / JNL — используется для перехода, если выполнено больше / равно / не меньше, чем инструкция.

JL / JNGE — используется для перехода, если удовлетворяется инструкция меньше / не больше / равно.

JLE / JNG — используется для перехода, если выполнено меньше / равно / если не больше, чем инструкция.

JNC — используется для прыжка, если нет флага переноса (CF = 0)

JNE / JNZ — используется для перехода, если не равен / нулевой флаг ZF = 0

JNO — используется для перехода, если нет флага переполнения OF = 0

JNP / JPO — используется для перехода, если не четность / четность нечетная PF = 0

JNS — используется для прыжка, если не знак SF = 0

JO — используется для перехода, если флаг переполнения OF = 1

JP / JPE — используется для перехода, если четность / четность даже PF = 1

JS — Используется для перехода, если флаг знака SF = 1

Инструкция по управлению процессором

Эти инструкции используются для управления действиями процессора путем установки / сброса значений флага.

Ниже приведены инструкции в этой группе:

-

STC — используется для установки флага переноса CF на 1

-

CLC — используется для сброса / сброса флага переноса CF на 0

-

CMC — используется для установки дополнения в состоянии флага переноса CF.

-

STD — используется для установки флага направления DF на 1

-

CLD — используется для сброса / сброса флага направления DF на 0

-

STI — используется для установки флага разрешения прерывания на 1, т. Е. Для включения входа INTR.

-

CLI — используется для сброса флага разрешения прерываний на 0, т. Е. Для отключения входа INTR.

STC — используется для установки флага переноса CF на 1

CLC — используется для сброса / сброса флага переноса CF на 0

CMC — используется для установки дополнения в состоянии флага переноса CF.

STD — используется для установки флага направления DF на 1

CLD — используется для сброса / сброса флага направления DF на 0

STI — используется для установки флага разрешения прерывания на 1, т. Е. Для включения входа INTR.

CLI — используется для сброса флага разрешения прерываний на 0, т. Е. Для отключения входа INTR.

Инструкции по контролю итерации

Эти инструкции используются для выполнения данных инструкций несколько раз. Ниже приведен список инструкций в этой группе —

-

LOOP — используется для зацикливания группы команд до тех пор, пока условие не будет удовлетворено, то есть CX = 0

-

LOOPE / LOOPZ — используется для зацикливания группы команд до тех пор, пока она не удовлетворит ZF = 1 и CX = 0

-

LOOPNE / LOOPNZ — используется для зацикливания группы команд до тех пор, пока она не удовлетворит ZF = 0 и CX = 0

-

JCXZ — используется для перехода к указанному адресу, если CX = 0

LOOP — используется для зацикливания группы команд до тех пор, пока условие не будет удовлетворено, то есть CX = 0

LOOPE / LOOPZ — используется для зацикливания группы команд до тех пор, пока она не удовлетворит ZF = 1 и CX = 0

LOOPNE / LOOPNZ — используется для зацикливания группы команд до тех пор, пока она не удовлетворит ZF = 0 и CX = 0

JCXZ — используется для перехода к указанному адресу, если CX = 0

Инструкции по прерыванию

Эти инструкции используются для вызова прерывания во время выполнения программы.

-

INT — Используется для прерывания программы во время выполнения и вызова указанной службы.

-

INTO — используется для прерывания программы во время выполнения, если OF = 1

-

IRET — используется для возврата из службы прерываний в основную программу

INT — Используется для прерывания программы во время выполнения и вызова указанной службы.

INTO — используется для прерывания программы во время выполнения, если OF = 1

IRET — используется для возврата из службы прерываний в основную программу

Микропроцессор — 8086 прерываний

Прерывание — это метод создания временной остановки во время выполнения программы и позволяет периферийным устройствам получать доступ к микропроцессору. Микропроцессор отвечает на это прерывание ISR (подпрограммой обработки прерываний), которая представляет собой короткую программу для инструктирования микропроцессора о том, как обрабатывать прерывание.

На следующем рисунке показаны типы прерываний, которые мы имеем в микропроцессоре 8086 —

Аппаратные прерывания

Аппаратное прерывание вызывается любым периферийным устройством, посылая сигнал через указанный контакт в микропроцессор.

8086 имеет два вывода аппаратного прерывания, то есть NMI и INTR. NMI является немаскируемым прерыванием, а INTR является маскируемым прерыванием, имеющим более низкий приоритет. Еще один связанный контакт прерывания — это INTA, называемый подтверждением прерывания.

NMI

Это один немаскируемый вывод прерывания (NMI), имеющий более высокий приоритет, чем маскируемый вывод запроса прерывания (INTR), и он имеет прерывание типа 2.

Когда это прерывание активировано, происходят следующие действия:

-

Завершает текущую инструкцию, которая выполняется.

-

Помещает значения регистра флага в стек.

-

Выдвигает значение CS (сегмент кода) и значение IP (указатель инструкции) адреса возврата в стек.

-

IP загружается из содержимого слова местоположения 00008H.

-

CS загружается из содержимого следующего слова местоположения 0000AH.

-

Флаг прерывания и флаг прерывания сбрасываются в 0.

Завершает текущую инструкцию, которая выполняется.

Помещает значения регистра флага в стек.

Выдвигает значение CS (сегмент кода) и значение IP (указатель инструкции) адреса возврата в стек.

IP загружается из содержимого слова местоположения 00008H.

CS загружается из содержимого следующего слова местоположения 0000AH.

Флаг прерывания и флаг прерывания сбрасываются в 0.

ВВЕДЕНИ

INTR является маскируемым прерыванием, потому что микропроцессор будет прерываться только в том случае, если прерывания разрешены с использованием команды установки флага прерывания. Его не следует включать с помощью команды очистки флага прерывания.

Прерывание INTR активируется портом ввода / вывода. Если прерывание включено и NMI отключено, то микропроцессор сначала завершает текущее выполнение и дважды посылает «0» на вывод INTA. Первый «0» означает, что INTA информирует внешнее устройство о готовности, а во время второго «0» микропроцессор получает 8-битный, скажем, X, от программируемого контроллера прерываний.

Эти действия предпринимаются микропроцессором —

-

Сначала завершает текущую инструкцию.

-

Активирует выход INTA и получает тип прерывания, скажем, X.

-

Значение регистра флага, значение CS возвращаемого адреса и значение IP возвращаемого адреса помещаются в стек.

-

Значение IP загружается из содержимого слова местоположения X × 4

-

CS загружается из содержимого местоположения следующего слова.

-

Флаг прерывания и флаг прерывания сбрасываются на 0

Сначала завершает текущую инструкцию.

Активирует выход INTA и получает тип прерывания, скажем, X.

Значение регистра флага, значение CS возвращаемого адреса и значение IP возвращаемого адреса помещаются в стек.

Значение IP загружается из содержимого слова местоположения X × 4

CS загружается из содержимого местоположения следующего слова.

Флаг прерывания и флаг прерывания сбрасываются на 0

Программные прерывания

Некоторые инструкции вставляются в нужную позицию в программу для создания прерываний. Эти инструкции по прерыванию можно использовать для проверки работы различных обработчиков прерываний. Включает в себя —

INT- инструкция прерывания с номером типа

Это 2-байтовая инструкция. Первый байт предоставляет код операции, а второй байт — номер типа прерывания. В этой группе 256 типов прерываний.

Его выполнение включает в себя следующие этапы —

-

Значение регистра флага помещается в стек.

-

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

-

IP загружается из содержимого слова местоположения «номер типа» × 4

-

CS загружается из содержимого местоположения следующего слова.

-

Флаг прерывания и Флаг ловушки сбрасываются на 0

Значение регистра флага помещается в стек.

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

IP загружается из содержимого слова местоположения «номер типа» × 4

CS загружается из содержимого местоположения следующего слова.

Флаг прерывания и Флаг ловушки сбрасываются на 0

Начальный адрес для прерывания типа 0 — 000000H, для прерывания типа 1 — 00004H, аналогично для типа 2 — 00008H и так далее. Первые пять указателей являются выделенными указателями прерывания. то есть

-

Прерывание ТИПА 0 представляет деление на нулевую ситуацию.

-

Прерывание ТИПА 1 представляет одношаговое выполнение во время отладки программы.

-

Прерывание типа 2 представляет немаскируемое прерывание NMI.

-

Прерывание ТИПА 3 представляет прерывание точки останова.

-

Прерывание ТИПА 4 представляет прерывание переполнения.

Прерывание ТИПА 0 представляет деление на нулевую ситуацию.

Прерывание ТИПА 1 представляет одношаговое выполнение во время отладки программы.

Прерывание типа 2 представляет немаскируемое прерывание NMI.

Прерывание ТИПА 3 представляет прерывание точки останова.

Прерывание ТИПА 4 представляет прерывание переполнения.

Прерывания от типа 5 до типа 31 зарезервированы для других усовершенствованных микропроцессоров, а прерывания от 32 до типа 255 доступны для аппаратных и программных прерываний.

INT 3-точка прерывания Инструкция по прерыванию

Это однобайтовая инструкция с кодом операции CCH. Эти инструкции вставляются в программу таким образом, что, когда процессор достигает этого уровня, он останавливает нормальное выполнение программы и выполняет процедуру точки останова.

Его выполнение включает в себя следующие этапы —

-

Значение регистра флага помещается в стек.

-

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

-

IP загружается из содержимого слова местоположения 3 × 4 = 0000CH

-

CS загружается из содержимого местоположения следующего слова.

-

Флаг прерывания и Флаг ловушки сбрасываются на 0

Значение регистра флага помещается в стек.

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

IP загружается из содержимого слова местоположения 3 × 4 = 0000CH

CS загружается из содержимого местоположения следующего слова.

Флаг прерывания и Флаг ловушки сбрасываются на 0

INTO — прерывание по команде переполнения

Это однобайтовая инструкция и их мнемоническое INTO . Код операции для этой инструкции — CEH. Как следует из названия, это условная команда прерывания, то есть она активна, только когда флаг переполнения установлен в 1 и переходит к обработчику прерываний, чей номер типа прерывания равен 4. Если флаг переполнения сбрасывается, то выполнение продолжается до Следующая инструкция.

Его выполнение включает в себя следующие этапы —

-

Значения регистров флага помещаются в стек.

-

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

-

IP загружается из содержимого слова местоположения 4 × 4 = 00010H

-

CS загружается из содержимого местоположения следующего слова.

-

Флаг прерывания и флаг Trap сбрасываются на 0

Значения регистров флага помещаются в стек.

Значение CS адреса возврата и значение IP адреса возврата помещаются в стек.

IP загружается из содержимого слова местоположения 4 × 4 = 00010H

CS загружается из содержимого местоположения следующего слова.

Флаг прерывания и флаг Trap сбрасываются на 0

Микропроцессор — 8086 режимов адресации

Различные способы обозначения исходного операнда в инструкции известны как режимы адресации . В программировании 8086 есть 8 различных режимов адресации —

Режим немедленной адресации

Режим адресации, в котором операнд данных является частью самой инструкции, называется режимом немедленной адресации.

пример

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFH

Зарегистрировать режим адресации

Это означает, что регистр является источником операнда для инструкции.

пример

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AX

Режим прямой адресации

Режим адресации, в котором эффективный адрес ячейки памяти записывается непосредственно в инструкции.

пример

MOV AX, [1592H], MOV AL, [0300H]

Зарегистрировать режим косвенной адресации

Этот режим адресации позволяет адресовать данные в любом месте памяти через адрес смещения, который хранится в любом из следующих регистров: BP, BX, DI & SI.

пример

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}

Основанный режим адресации

В этом режиме адресации адрес смещения операнда задается суммой содержимого регистров BX / BP и смещения 8 бит / 16 бит.

пример

MOV DX, [BX+04], ADD CL, [BX+08]

Режим индексированной адресации

В этом режиме адресации адрес смещения операндов находится путем сложения содержимого регистра SI или DI и смещения 8-бит / 16-бит.

пример

MOV BX, [SI+16], ADD AL, [DI+16]

Режим адресации на основе индекса

В этом режиме адресации адрес смещения операнда вычисляется путем суммирования базового регистра с содержимым регистра индекса.

пример

ADD CX, [AX+SI], MOV AX, [AX+DI]

На основе индексируется с режимом смещения

В этом режиме адресации смещение операндов вычисляется путем добавления содержимого базового регистра. Индекс регистрирует содержимое и смещение 8 или 16 бит.

пример

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]

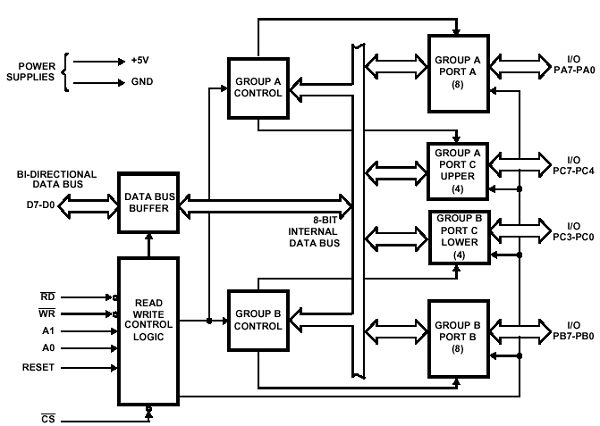

Обзор многопроцессорной конфигурации

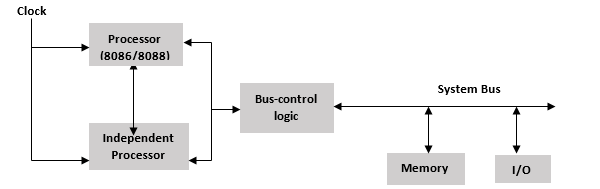

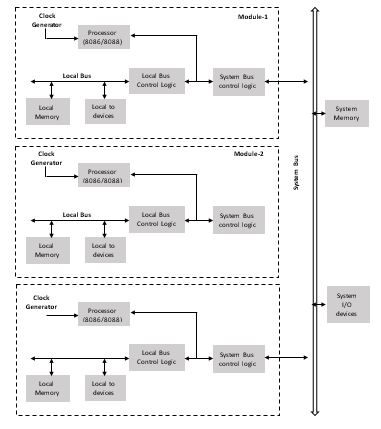

Мультипроцессор означает множественный набор процессоров, которые выполняют инструкции одновременно. Существует три основных многопроцессорных конфигурации.

- Конфигурация сопроцессора

- Тесно связанная конфигурация

- Слабосвязанная конфигурация

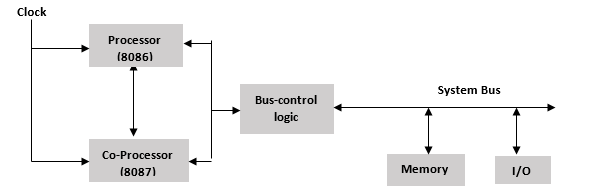

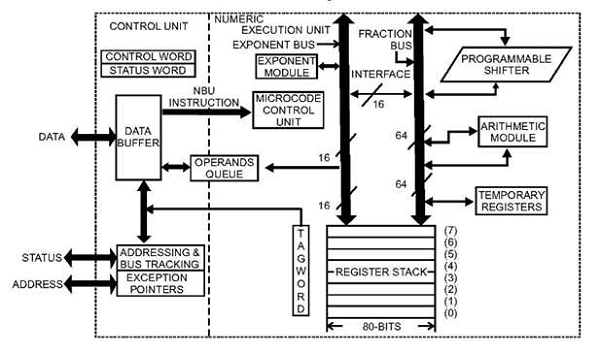

Конфигурация сопроцессора

Копроцессор — это специально разработанная схема на микропроцессорном чипе, которая может очень быстро выполнить ту же задачу, которую выполняет микропроцессор. Это снижает нагрузку на основной процессор. Сопроцессор использует одну и ту же память, систему ввода-вывода, шину, управляющую логику и тактовый генератор. Сопроцессор выполняет специализированные задачи, такие как математические вычисления, графическое отображение на экране и т. Д.