8086 был первым 16-разрядным микропроцессором, доступным в 40-контактном DIP (Dual Inline Package) чипе. Теперь давайте подробно обсудим конфигурацию контактов микропроцессора 8086.

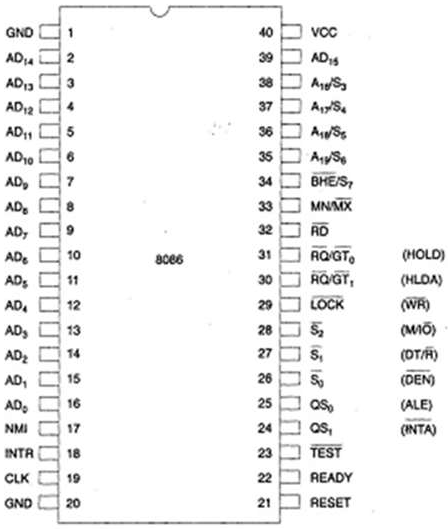

8086 Pin Diagram

Вот схема контактов микропроцессора 8086 —

Давайте теперь обсудим сигналы в деталях —

Сигналы питания и частоты

Он использует питание 5 В постоянного тока на выводе V CC 40 и заземление на выводах 1 и 20 V SS для своей работы.

Тактовый сигнал

Тактовый сигнал подается через контакт 19. Он обеспечивает синхронизацию процессора для операций. Его частота различна для разных версий: 5 МГц, 8 МГц и 10 МГц.

Адрес / шина данных

AD0-AD15. Это 16 адрес / шина данных. AD0-AD7 переносит байтовые данные младшего разряда, а AD8AD15 переносит байтовые данные старшего порядка. В течение первого тактового цикла он переносит 16-битный адрес и после этого переносит 16-битные данные.

Адрес / статус шины

A16-A19 / S3-S6. Это 4 адреса / статус шины. В течение первого тактового цикла он несет 4-битный адрес, а затем передает сигналы состояния.

S7 / ППТ

BHE расшифровывается как Bus High Enable. Он доступен на выводе 34 и используется для индикации передачи данных с использованием шины данных D8-D15. Этот сигнал низкий в течение первого тактового цикла, после чего он активен.

Читать ( $ \ overline {RD} $ )

Он доступен на выводе 32 и используется для считывания сигнала для операции чтения.

готовы

Он доступен на выводе 22. Это сигнал подтверждения от устройств ввода-вывода о том, что данные передаются. Это активный высокий сигнал. Когда он высокий, это означает, что устройство готово для передачи данных. Когда оно низкое, это указывает на состояние ожидания.

СБРОС

Он доступен на выводе 21 и используется для возобновления выполнения. Это заставляет процессор немедленно прекратить свою текущую деятельность. Этот сигнал является активным высоким в течение первых 4 тактов для СБРОСА микропроцессора.

ВВЕДЕНИ

Он доступен на выводе 18. Это сигнал запроса прерывания, который дискретизируется в течение последнего тактового цикла каждой команды, чтобы определить, рассматривал ли процессор это как прерывание или нет.

NMI

Он обозначает немаскируемое прерывание и доступен на выводе 17. Это вход, инициируемый фронтом, который вызывает запрос прерывания для микропроцессора.

$ \ Overline {TEST} $

Этот сигнал похож на состояние ожидания и доступен на выводе 23. Когда этот сигнал высокий, то процессор должен ждать состояния IDLE, иначе выполнение продолжается.

MN / $ \ overline {MX} $

Он обозначает Minimum / Maximum и доступен на выводе 33. Он указывает, в каком режиме должен работать процессор; когда он высокий, он работает в минимальном режиме и наоборот.

INTA

Это сигнал подтверждения прерывания и идентификатор, доступный на выводе 24. Когда микропроцессор получает этот сигнал, он подтверждает прерывание.

ALE

Он обозначает защелку разрешения адреса и доступен на выводе 25. Положительный импульс генерируется каждый раз, когда процессор начинает какую-либо операцию. Этот сигнал указывает на наличие действительного адреса в адресной строке / строке данных.

DEN

Он обозначает Data Enable и доступен на выводе 26. Он используется для включения Transreceiver 8286. Transreceiver — это устройство, используемое для отделения данных от адреса / шины данных.

DT / R

Он обозначает сигнал передачи / приема данных и доступен на выводе 27. Он определяет направление потока данных через трансивер. Когда он высокий, данные передаются и наоборот.

М / МО

Этот сигнал используется для различения операций памяти и ввода / вывода. Когда он высокий, это указывает на операцию ввода / вывода, а когда он низкий, указывает на работу памяти. Он доступен на контакте 28.

WR

Он обозначает сигнал записи и доступен на выводе 29. Он используется для записи данных в память или устройство вывода в зависимости от состояния сигнала M / IO.

HLDA

Он обозначает сигнал подтверждения приема и доступен на выводе 30. Этот сигнал подтверждает сигнал HOLD.

ДЕРЖАТЬ

Этот сигнал указывает процессору, что внешние устройства запрашивают доступ к шинам адреса / данных. Он доступен на контакте 31.

QS 1 и QS 0

Это сигналы состояния очереди, которые доступны на контактах 24 и 25. Эти сигналы обеспечивают состояние очереди команд. Их условия показаны в следующей таблице —

| QS 0 | QS 1 | Статус |

|---|---|---|

| 0 | 0 | Нет операции |

| 0 | 1 | Первый байт кода операции из очереди |

| 1 | 0 | Очистить очередь |

| 1 | 1 | Последующий байт из очереди |

S 0 , S 1 , S 2

Это сигналы состояния, которые обеспечивают состояние работы, которое используется контроллером шины 8288 для генерации сигналов управления памятью и вводом / выводом. Они доступны на контактах 26, 27 и 28. Ниже приведена таблица, показывающая их статус —

| S 2 | S 1 | S 0 | Статус |

|---|---|---|---|

| 0 | 0 | 0 | Подтверждение прерывания |

| 0 | 0 | 1 | Чтение ввода / вывода |

| 0 | 1 | 0 | I / O Write |

| 0 | 1 | 1 | стой |

| 1 | 0 | 0 | Извлечение кода операции |

| 1 | 0 | 1 | Чтение памяти |

| 1 | 1 | 0 | Запись в память |

| 1 | 1 | 1 | пассивный |

ЗАМОК

Когда этот сигнал активен, он указывает другим процессорам не просить ЦП покинуть системную шину. Он активируется с помощью префикса LOCK любой инструкции и доступен на выводе 29.

RQ / GT 1 и RQ / GT 0

Это сигналы Запроса / Предоставления, используемые другими процессорами, запрашивающими ЦПУ освободить системную шину. Когда ЦП получает сигнал, он отправляет подтверждение. RQ / GT 0 имеет более высокий приоритет, чем RQ / GT 1 .