DMA означает прямой доступ к памяти. Он разработан Intel для быстрой передачи данных. Это позволяет устройству передавать данные непосредственно в / из памяти без какого-либо вмешательства ЦП.

Используя контроллер DMA, устройство запрашивает у ЦП свои данные, адрес и управляющую шину, поэтому устройство может передавать данные непосредственно в / из памяти. Передача данных DMA начинается только после получения сигнала HLDA от CPU.

Как выполняются операции DMA?

Ниже приведена последовательность операций, выполняемых DMA —

-

Первоначально, когда какое-либо устройство должно отправить данные между устройством и памятью, оно должно отправить запрос DMA (DRQ) на контроллер DMA.

-

Контроллер DMA отправляет запрос удержания (HRQ) в ЦП и ожидает, пока ЦП утвердит HLDA.

-

Затем микропроцессор делит три состояния на всю шину данных, адресную шину и управляющую шину. ЦП покидает контроль над шиной и подтверждает запрос HOLD через сигнал HLDA.

-

Теперь процессор находится в состоянии HOLD, и контроллер DMA должен управлять операциями по шинам между процессором, памятью и устройствами ввода-вывода.

Первоначально, когда какое-либо устройство должно отправить данные между устройством и памятью, оно должно отправить запрос DMA (DRQ) на контроллер DMA.

Контроллер DMA отправляет запрос удержания (HRQ) в ЦП и ожидает, пока ЦП утвердит HLDA.

Затем микропроцессор делит три состояния на всю шину данных, адресную шину и управляющую шину. ЦП покидает контроль над шиной и подтверждает запрос HOLD через сигнал HLDA.

Теперь процессор находится в состоянии HOLD, и контроллер DMA должен управлять операциями по шинам между процессором, памятью и устройствами ввода-вывода.

Особенности 8257

Вот список некоторых выдающихся особенностей 8257 —

-

Он имеет четыре канала, которые можно использовать на четырех устройствах ввода-вывода.

-

Каждый канал имеет 16-битный адрес и 14-битный счетчик.

-

Каждый канал может передавать данные до 64 КБ.

-

Каждый канал может быть запрограммирован независимо.

-

Каждый канал может выполнять операции чтения чтения, записи записи и проверки операций передачи.

-

Он генерирует сигнал MARK для периферийного устройства о том, что было передано 128 байтов.

-

Это требует однофазных часов.

-

Его частота колеблется от 250 Гц до 3 МГц.

-

Он работает в 2 режимах, то есть в режиме Master и Slave .

Он имеет четыре канала, которые можно использовать на четырех устройствах ввода-вывода.

Каждый канал имеет 16-битный адрес и 14-битный счетчик.

Каждый канал может передавать данные до 64 КБ.

Каждый канал может быть запрограммирован независимо.

Каждый канал может выполнять операции чтения чтения, записи записи и проверки операций передачи.

Он генерирует сигнал MARK для периферийного устройства о том, что было передано 128 байтов.

Это требует однофазных часов.

Его частота колеблется от 250 Гц до 3 МГц.

Он работает в 2 режимах, то есть в режиме Master и Slave .

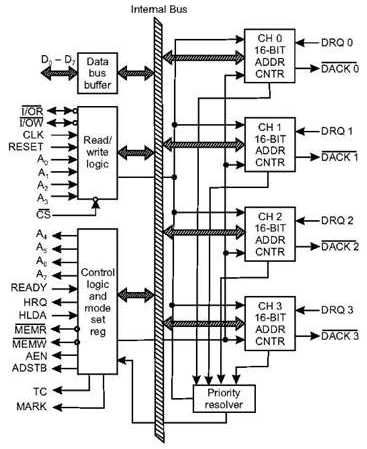

8257 Архитектура

На следующем изображении показана архитектура 8257 —

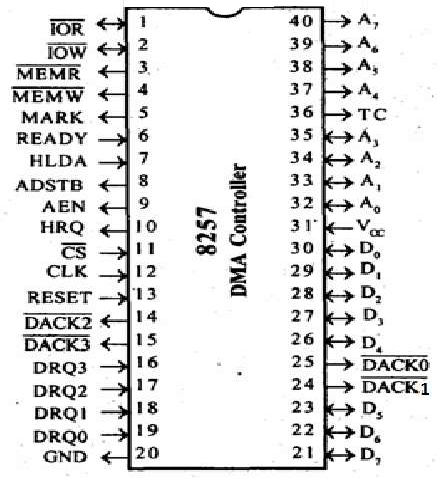

8257 Pin Описание

На следующем рисунке показана схема контактов контроллера прямого доступа к памяти 8257 —

DRQ 0 −DRQ 3

Это четыре отдельных канала ввода запроса DMA, которые используются периферийными устройствами для использования услуг DMA. Когда выбран режим с фиксированным приоритетом, то DRQ 0 имеет самый высокий приоритет, а DRQ 3 имеет самый низкий приоритет среди них.

DACK o — DACK 3

Это линии подтверждения активного низкого уровня DMA, которые обновляют запрашивающее периферийное устройство о состоянии их запроса ЦПУ. Эти линии также могут выступать в качестве стробирующих линий для запрашивающих устройств.

Д о — Д 7

Это двунаправленные линии передачи данных, которые используются для сопряжения системной шины с внутренней шиной данных контроллера DMA. В подчиненном режиме он переносит командные слова в 8257 и слово состояния из 8257. В основном режиме эти строки используются для отправки старшего байта сгенерированного адреса в защелку. Этот адрес дополнительно фиксируется с помощью сигнала ADSTB.

IOR

Это двунаправленная входная линия с тремя активными состояниями, которая используется ЦП для считывания внутренних регистров 8257 в подчиненном режиме. В основном режиме он используется для чтения данных с периферийных устройств во время цикла записи в память.

IOW

Это активная линия с тремя состояниями в двух направлениях, которая используется для загрузки содержимого шины данных в регистр 8-битного режима или в верхний / нижний байт 16-битного регистра адресов DMA или регистра подсчета терминалов. В режиме мастера он используется для загрузки данных на периферийные устройства во время цикла чтения памяти DMA.

CLK

Это сигнал тактовой частоты, который требуется для внутренней работы 8257.

СБРОС

Этот сигнал используется для сброса контроллера DMA путем отключения всех каналов DMA.

A o — A 3

Это четыре наименее значимые адресные строки. В подчиненном режиме они действуют как вход, который выбирает один из регистров для чтения или записи. В режиме master они являются четырьмя наименее значимыми строками вывода адресов памяти, сгенерированными 8257.

CS

Это линия выбора активных и низких фишек. В режиме Slave он разрешает операции чтения / записи в / из 8257. В режиме мастера он отключает операции чтения / записи в / из 8257.

А 4 — А 7

Это верхний полубайт младшего байтового адреса, сгенерированного DMA в режиме мастера.

ГОТОВЫ

Это активный высокий асинхронный входной сигнал, который подготавливает DMA путем вставки состояний ожидания.

HRQ

Этот сигнал используется для приема сигнала запроса удержания от устройства вывода. В подчиненном режиме он связан с линией входа DRQ 8257. В режиме Master он связан со входом HOLD ЦПУ.

HLDA

Это сигнал подтверждения удержания, который указывает контроллеру DMA, что шина была предоставлена запрашивающему периферийному устройству центральным процессором, когда он установлен в 1.

МЭМР

Это сигнал чтения из нехватки памяти, который используется для чтения данных из адресованных областей памяти во время циклов чтения DMA.

MEMW

Это сигнал трех активных состояний, который используется для записи данных в адресную ячейку памяти во время операции записи DMA.

ADST

Этот сигнал используется для преобразования старшего байта адреса памяти, сгенерированного контроллером DMA, в защелки.

АЕН

Этот сигнал используется для отключения адресной шины / шины данных.

TC

Он обозначает «Количество терминалов», которое указывает текущий цикл DMA для существующих периферийных устройств.

ОТМЕТКА

Знак будет активироваться после каждых 128 циклов или целых кратных с самого начала. Это указывает на то, что текущий цикл DMA является 128-м циклом с момента предыдущего вывода MARK на выбранное периферийное устройство.

V cc

Это сигнал мощности, необходимый для работы схемы.